# HPC insights DoD Supercomputing Resource Centers UGC Edition

AFRL • ARL • ARSC • ERDC • MHPCC • NAVY SUPERCOMPUTING FOR THE WARFIGHTER

LIVERING ADVANCED

*HPC Insights* is a semiannual publication of the Department of Defense Supercomputing Resource Centers under the auspices of the High Performance Computing Modernization Program.

#### **Publication Team**

AFRL DSRC, Wright-Patterson Air Force Base, OH Joan Henley Chuck Abruzzino

ARL DSRC, Aberdeen Proving Ground, MD Debbie Thompson Brian Simmonds

ARSC DSRC, Fairbanks, AK Debra Damron Mary Haley

ERDC DSRC, Vicksburg, MS Rose J. Dykes

MHPCC DSRC, Maui, HI Jeff Schmidt Betty Duncan

Navy DSRC, Stennis Space Center, MS Christine Cuicchi Lynn Yott

HPCMPO, Lorton, VA Deborah Schwartz Sheryl Caramanzana Leah Glick

MANAGING EDITOR Rose J. Dykes, ERDC DSRC

DESIGN/LAYOUT Betty Watson, ACE-IT

COVER DESIGN Chandra "Pat" Caldwell, ACE-IT

The contents of this publication are not to be used for advertising, publication, or promotional purposes. Citation of trade names does not constitute an official endorsement or approval of the use of such commercial products. Any opinions, findings, conclusions, or recommendations expressed in this publication are those of the author(s) and do not necessarily reflect the views of the DoD.

Approved for Public Release; Distribution Is Unlimited.

# Contents

| DoD Supercomputing Resource Centers<br>Making the Supercomputer Wait on the Scientist | 1  |

|---------------------------------------------------------------------------------------|----|

| AFRL DSRC                                                                             |    |

| From the Director's Desk – Frank Witzeman                                             | 2  |

| ARL DSRC                                                                              |    |

| From the Director's Desk – Charles J. Nietubicz                                       | 3  |

| DRE Portal                                                                            |    |

| ARSC DSRC                                                                             |    |

| From the Director's Desk – Frank Williams                                             | 5  |

| Increasing Capabilities of Front-End Nodes to High Performance                        |    |

| Computing Resources                                                                   | 6  |

| ERDC DSRC                                                                             |    |

| From the Director's Desk – Dr. Robert S. Maier                                        | 8  |

| New Record Set on Diamond in Quantum Turbulence Simulations                           | 9  |

| MHPCC DSRC                                                                            |    |

| From the Director's Desk – David Morton                                               | 11 |

| MHPCC DSRC's Newest Supercomputer, Mana, Goes Green                                   |    |

| HPCMP Challenge Projects Have Mana's Lights Flashing                                  |    |

| MHPCC DSRC HPCMP DHPI Award Gives Rise to Kaku                                        |    |

| for the AMOS Site                                                                     |    |

| Maui Energy Improvement Initiative (MEII)                                             | 13 |

| NAVY DSRC                                                                             |    |

| From the Director's Desk – Tom Dunn                                                   |    |

| Infrastructure Upgrades Prepare Navy DSRC for the Future                              | 15 |

| DAAC                                                                                  |    |

| From the Director's Desk – Mike Stephens                                              |    |

| ParaView Client-Server on Crays at the ERDC DSRC                                      | 17 |

| Help for the HPC User                                                                 |    |

| Graphical User Interface to Create GAMESS Input Files                                 |    |

| from Within VMD                                                                       |    |

| User Interface Toolkit (UIT) v3.1                                                     |    |

| ASC Users to HPCMP Realm Consolidation                                                |    |

| External Login Servers Enhance EINSTEIN Capabilities                                  |    |

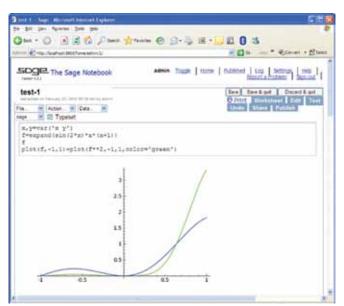

| Python for Scientific and Parallel Computing                                          | 25 |

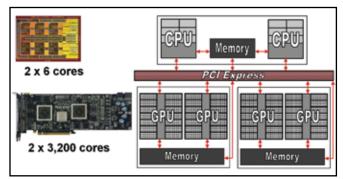

| Investigation of Algorithms for Hybrid Multicore/Many-Core<br>Architectures           | 20 |

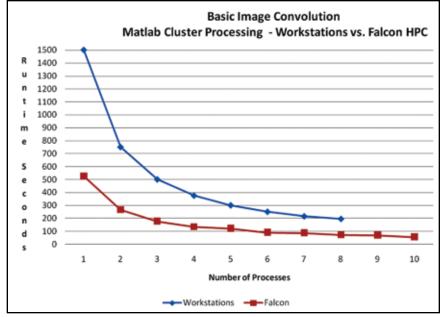

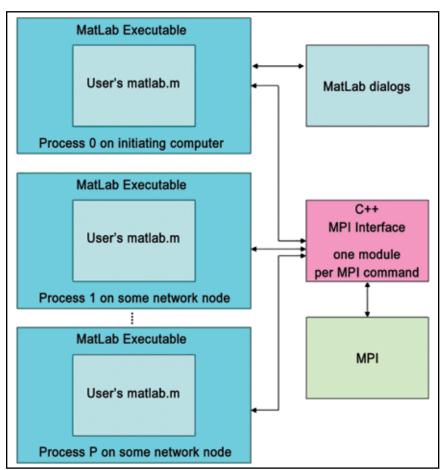

| Parallel MATLAB Without Toolbox Licenses Using Standard                               | 29 |

| MPI Implementations                                                                   | 31 |

| Launch of the Storage Initiative                                                      |    |

| New Web Site Unveiled to Guide Allocation Requests with                               |    |

| TI-10 Benchmarking Times                                                              | 35 |

| Tuning Application Performance on the Cray XT Without                                 |    |

| Modifying the Code                                                                    |    |

| HPCMP Sustained Systems Performance Test                                              |    |

| MPI IO on the Cray XT Series                                                          | 40 |

| Announcements                                                                         |    |

| SC10                                                                                  | 40 |

**About the Cover:** The picture on the front shows a U.S. Air Force Tech. Sgt. sitting on the ramp of a C-17 Globemaster III aircraft while flying over the mountains of Afghanistan after an airdrop mission in February 2010. U.S. Air Force photo by Staff Sgt. Angelita Lawrence

# DoD Supercomputing Resource Centers Making the Supercomputer Wait on the Scientist

#### By Brad Comes, HPC Centers Project Manager

Hindsight is 20/20, and we won't know for sure until we can look back; but we believe the High Performance Computing Modernization Program (HPCMP) is at a tipping point. Historically, our challenge has been to keep pace with the computational demands of scientists and engineers in the Department of Defense (DoD). Fundamentally, this meant acquiring and deploying the latest commercially available high performance computers. Our computational capabilities have nearly doubled every year. Here's where the tipping point comes in. Recent forecasts from the HPCMP annual requirements surveys indicate that we're approaching the ability to meet the DoD's high performance computing "compute" requirements. What does this mean? Our first reaction was that we'll reduce the rate of deployment of new supercomputer capabilities. However, we surveyed the HPC user community, and the data revealed a requirement we never thought we would have had the luxury of addressing-to increase the productivity of the scientist versus the productivity of the computer. Our strategy to enhance science and engineer productivity has evolved with two initiatives-improved time-to-solution and seamless workflow.

In concept, improved time-to-solution is achieved by improving the traditional batch job submission environment to something approaching interactive computing. I say "something approaching" because interactive supercomputing is a ways off. But, we need to move in that direction. Doing this requires a change in the way we operate our supercomputers and measure success. Currently, people wait on the very precious supercomputer. We have to create an environment where the computers are waiting on the people. Historically, we have strived for 70-80 percent system utilization. The other 20-30 percent is overhead from downtime events and unavoidable gaps in job scheduling. Anything below 70-80 percent has been perceived as if we were doing something wrong: we didn't have enough users on the system; we had too much system downtime; we weren't efficiently scheduling jobs; and always looming in the wings is the inevitable conclusion-if you're only using 70 percent of what you have, why do you need more? We have to break the multiple decade mentality that we can't afford to let a CPU cycle go unused. In pursuit of significantly increasing the productivity of our highly educated, skilled, and expensive workforce, we need to instead strive for high scientist and engineer utilization rates. Scientists and engineers should not have to wait for the computers; the computers should be waiting

for them—likely resulting in HPC system utilization rates at or below the 50th percentile. One service contributing to this goal that you'll find available by the time this is published is the Advance Reserva-

Brad Comes HPC Centers Project Manager

tion System (ARS); most all systems in the HPCMP will have an ARS capability for end-users to schedule a predetermined time to start a job. This is a first step toward making the computer wait on the scientist.

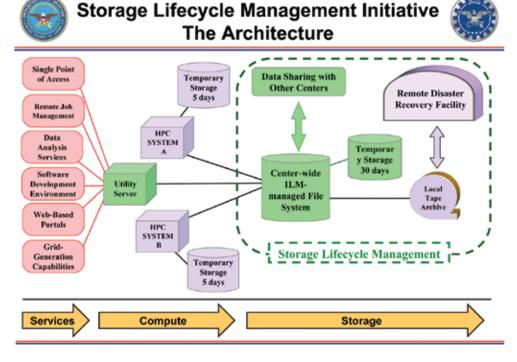

Supercomputers are the crown jewel in a computing infrastructure, but they have never been tightly integrated into their surroundings. The functionalities associated with desktop and server room computing exploded while supercomputers remained pretty much batch engines with command-line prompts. This has created gaps in the user's workflow that again significantly contributes to inefficiencies in end-user productivity. The HPCMP is focusing on closing this gap. The most significant nearterm initiatives that will contribute toward this are the Storage Initiative (SI) and the Common Utility Enhancement Services (CUES). Services you can expect to see in Fiscal Year 2011 associated with the SI and CUES are 30-day working directories (versus the current 5), an information lifecycle management system for archived data, remote visualization services, and remote job management. Longer term projects include the delivery of interactive grid-generation capabilities, an extensive software development environment, a single sign-on capability, and Web-based portals that connect the desktop to the supercomputer.

The HPCMP's first reaction to our out-year projections of compute requirements versus compute capabilities suggested that we had achieved our mission of "HPC modernization." All we had to do now was retain our edge. However, upon a closer look, we realized that we had another huge opportunity—user productivity. As a result, we are now leveraging lessons learned from our challenges of the past into mature processes required to sustain the core HPC compute capability while we embark on this new challenge—making the supercomputer wait on the scientist.

# AFRL DSRC

# Air Force Research Laboratory DoD Supercomputing Resource Center

# From the Director's Desk – Frank Witzeman

The Technology Insertion 2010 (TI-10) award, delayed over 2 months, was announced with anticipated excitement within the AFRL DSRC—a new 43,712core next-generation Cray system will be coming to Wright Patterson Air Force Base this summer! It has been a long time since a Cray system was operational in our facility, and we're looking forward to a renewed, successful partnership with Cray Inc. in providing over 400 teraflops/sec to our users.

I recall that it was quite a challenge in 1990 to exploit the latest high performance computing (HPC) technology to calculate the complex fluid dynamic phenomena over aircraft components (e.g., wing sections). Typical turnaround times were assumed on the order of months to get meaningful results. Ten years later in 2000, reasonable turnaround times of days were being realized for fully turbulent, transonic flow over entire aircraft configurations. For those lucky enough to get most of the HPC system (about 1000 processors at that time), the calculations could be done in a matter of hours. Now in 2010, we have more computational power than we could have imagined 10-20 years ago, and we might expect solutions in a matter of minutes. Despite the rapid advances in HPC technology, however, we are still experiencing a relatively constant time-tosolution for our most demanding computational work.

There exist a number of reasons why we're not accelerating time-to-solution. From one perspective, preand postprocessing capabilities have not experienced necessary developments targeted for HPC applications and architectures. Many of these capabilities are best suited for the desktop or workstation environments, so there's no driving force to bring them into the HPC realm. Another issue is related to user applications that do not scale well. The applications themselves consist of the input/output data ("models") and analysis software ("codes") that quickly reach limits in terms of communications overhead where the problem being solved can only be partitioned across a reasonable set of cores or nodes before the computational time becomes swamped by the interconnect communication time. Users prefer to stay below these limits, thereby reducing the size of their applications to perhaps relatively low core counts. A related aspect is that users themselves do not scale well because they can easily become overwhelmed by the amount of data generated from massive computational problems. It has become easier to piece together several applications in order to better manage

smaller data sets than one enormous one (and get faster turnaround for each smaller application instead of waiting for one huge one).

More reasons have surfaced, such as the general lack of scalable software/

Frank Witzeman Director, AFRL DSRC

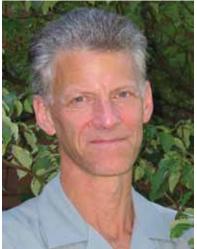

codes, and they all need to be investigated to determine how we will move forward in HPC and supercomputing. Are we satisfied with our current paradigm, that is, to continue to operate increasingly larger systems to accommodate growing workloads of relatively small core-count jobs? Or, should we take a fresh look at how we can encourage and expand large core-count jobs, on the order of tens of thousands of cores? Do we expect a reasonable mix of small (some tiny by today's standards) and large jobs that stretch the imagination of our HPC architectures? For reference, about 92 percent of all jobs on our SGI Altix 9000-core Hawk system use less than 100 cores and about 3 percent use 400 cores or more. An expectation 10 years ago might have been that maybe a third of our jobs in 2010 would consist of at least 1000 cores because our HPC systems would be capable of handling the workload.

As I think back to the early days of the HPCMP and think ahead to the possibilities, I am eager to learn more about our users' thoughts on the issues of HPC and supercomputing. I am aware of some anecdotal evidence that there are users eager to run ten thousand 1-core jobs on the new architectures, as well as users ready to scale up single applications to 10,000 cores. We need to be prepared to handle the anticipated full spectrum of jobs, and we can only do that by staying intimately connected to the user community.

# ARL DSRC

# Army Research Laboratory DoD Supercomputing Resource Center From the Director's Desk – Charles J. Nietubicz.

Hello again. It always gives me great pleasure to talk to you through HPC Insights and briefly mention the exciting activities ongoing at the ARL DSRC and the new directions in which we are heading. The management and staff here are proud to play a part in the successful HPCMP and trust that we are providing you the current, and working on the anticipated, services that you need. Our collective success comes from the hard work, dedication, and vision of many people. The ultimate success is measured in what you, the HPCMP user community, are able to provide to the warfighter in sophisticated weapons development and evaluation, made possible in part through the resources of the HPCMP. However, while we have had much success, we cannot rest with the status quo and need to continually look for how we can modernize, improve, be responsive, and create a future environment that rivals all that has come before now. It was not long ago that an Ethernet-connected workstation (some of you may remember that thick yellow cable running from office to office) interfacing with Cray supercomputers (the HPC standard in the late 80s, early 90s) was considered leading edge, top of the line, king of the road. We have come a long way since then and made great progress in solving some complex problems, but I see the future as being even more exciting. What is that future? I believe we will develop a new HPC world focused on access to HPC by nonexpert users, i.e., those engineers and scientists who need answers, not a new education. How can this happen? Through concepts like HPC cloud computing; HPC from user desktop environments; access via Web and graphical user interfaces; projects like the DRE Portal; next-generation DREN and handheld devices; data storage and retrieval from anywhere, anytime; and knowledge through information and data fusion. Now, I did not say this would be easy. Stating a vision is easy; accomplishing that vision is often hard. As the question is sometimes asked (nonliterally), "How do you eat an elephant?" - the answer comes back, "One bite at a time." So, that is how we can go about achieving our vision for HPC. Some of the "bites" are included in this issue of HPC Insights.

In the fall issue, I described some initial efforts we were beginning with the HPCMP Office (HPCMPO) on the development of a transparent access to HPC for Matlab users. This project is called the DRE Portal project, and we can use your help. See the call for participation on page 4; if you see Dr. Pat Collins walking the halls at the User Advocacy Group meeting, please let him know your thoughts on this subject. We are also researching a Microsoft HPC capability. Stop us in the halls at the Users Group Conference to discuss. We

*Charles J. Nietubicz*, Director, ARL DSRC

would very much like to get your thoughts and ideas in this area.

You may have heard some initial comments about the new HPCMP Storage Initiative originally developed to replace the end-of-life tape library. The initiative has expanded to include much more than its original goal and now includes looking at a standard storage architecture, infrastructure upgrades, and utility servers throughout the HPCMP. A full team from all Centers, representatives from the HPCMPO, and industry and user representatives are involved. Please take a look at the article (page 33) that provides some of the emerging details.

A new and emerging technology is the potential use of accelerators in the HPC arena. Where and how they fit is not exactly known, but we are beginning to investigate. This is not unlike the investigations we undertook in the 2000 time frame with cluster computers. Hybrid systems comprised of multicore and many-core configurations is an interesting technology that needs to be examined and understood. We need to see what works and what does not. Dr. David Richie and others are exploring these questions and have provided a good summary in their article "Investigations of Algorithms for Hybrid Multicore/Many-Core Architectures" found on page 29.

We would encourage you to take a look at the articles I have mentioned and feel free to contact the ARL DSRC with any questions or comments.

# ARL DSRC

# **DRE Portal**

#### By Steve Thompson, ARL DSRC Sortware Engineer

Would you like to use the power of many processors without needing to learn Linux?

If so, you will be interested to know that the ARL DSRC and the HPCMPO are working on a portal that will bring the power of high performance computing (HPC) to your Desktop. Currently, we are in the pilot phase of development as we work to define possible technologies and specify requirements. Matlab is our initial test application, with other applications to be made available later.

This portal is designed to bring HPC into your environment and, therefore, make HPC easier to use. Our goal is to provide an environment where you can use your familiar desktop interface to run an application, such as Matlab, yet harness the power of multiple processors. This will provide the ability to complete your computations much faster or allow for multiple parametric studies in the same time frame. This portal will be known as the DRE (Defense, Research, and Engineering) Portal.

Does this sound interesting to you? If so, you can help us in two ways:

(1) We need feedback from DoD Matlab users (especially those not currently using the DSRCs) as to how much you would envision using this portal when it becomes available.

(2) We need interested users to help with initial testing and shakeout of the pilot system to ensure that it will be robust enough to handle your computational needs.

Another technology that the ARL DSRC is investigating is the Microsoft (MS) HPC Server. Microsoft has made a significant investment in developing a massively parallel HPC server version of its commercial Operating System. This investment is showing up in many commercial sites for technical applications and cloud configurations (reconfigurable servers). ARL will be standing up hardware resources in conjunction with MS in an effort to provide computational cycles to MS applications, make use of MS development tools, and allow for seamless desktop to supercomputer integration.

Please give us your feedback by e-mailing us at dreportal@arl.army.mil.

# **ARSC DSRC**

# Arctic Region Supercomputing Center DoD Supercomputing Resource Center

#### From the Director's Desk – Frank Williams

The ARSC DSRC is one of three Centers in the HPCMP to receive new Cray supercomputers under the HPCMP Technology Insertion process for 2010.

With the installation of the ARSC DSRC's new 11,648 compute core Cray system this summer, DoD HPCMP users can access the newest in custom interconnect and chip technologies for their computational campaigns.

The 88,000-square-foot National Petascale Computing Facility in Champaign, IL, includes a 20,000-square-foot data center with an additional 10,000 square feet of raised floor for other infrastructure

The suite of new machines will be located in the Petascale Computing Facility (PCF) of the National Center for Supercomputing Applications (NCSA) at the University of Illinois.

Once installed, the systems will be remotely operated by the ARSC DSRC staff in Fairbanks and will eventually include a platform for Common Utility Enhancement Services (CUES). The ARSC DSRC is taking the lead in the programwide CUES effort aimed at increasing the functionality provided to users for postprocessing as well as an integrated archival storage system. Locating the new ARSC DSRC systems in the PCF will provide a production-level demonstration of full-up remote operations that at the same time exceeds all of the high standards the ARSC DSRC requires for

*Frank Williams* Director, ARSC DSRC

user satisfaction and data security.

The new ARSC DSRC supercomputer is considered by Cray to be one of its next-generation supercomputing systems, code-named *Baker*. It will feature a new interconnect chipset known as *Gemini* as well as enhanced system software to boost performance and productivity.

In addition to the ARSC DSRC supercomputer, PCF will house *Blue Waters*, www.ncsa.illinois.edu/Blue-Waters/, a massive supercomputer funded by the National Science Foundation that will be capable of performing quadrillions of calculations every second.

The ARSC DSRC's partnership with one of the largest academic supercomputing centers in the U.S. will provide the HPCMP and its users with more opportunities for collaboration and shared use of technologies colocated at the National Center for Supercomputing Applications.

We also believe this venture will provide the Modernization Program with a venue conducive to developing strategic opportunities with other Federal agencies and especially the National Science Foundation. The NCSA Director Thom Dunning is very supportive of

The machine room of the National Petascale Computing Facility will house the ARSC DSRC TI-10 system, an 11,648-core nextgeneration Cray that will be operated from Fairbanks. Next year, NPCF will bring Blue Waters online as the first system of its kind to sustain one petaflop performance on a range of science and engineering applications

# ARSC DSRC

the partnership and is especially excited about working collaboratively to help the scientists and engineers supported by the DoD meet their research goals.

The ARSC DSRC is proud of its leadership role in connecting research, computing, and defense communities with the computers, data storage systems, high-speed networks, and next-generation experimental systems necessary for discovery in engineering and science.

# Increasing Capabilities of Front-End Nodes to High Performance Computing Resources

#### By Dr. Greg Newby, Chief Scientist, ARSC DSRC

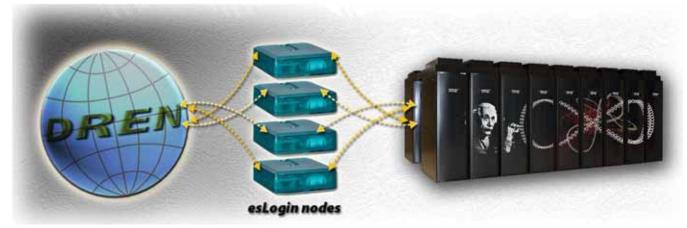

Three new types of nodes have been added to *Pingo*, the 3456-node Cray XT5 supercomputer at the ARSC DSRC. They are not computational nodes, administrative nodes, or storage nodes. While *Pingo*'s compute nodes have 8 CPU cores with 4 GB of memory each, these new nodes have 16 CPU cores, each with 8 GB of memory (128 GB total). Cray Inc. calls these external service login nodes (or esLogin, for short). They are early examples of what the HPCMP calls utility servers. Concepts and practices of utility servers are being developed by the HPCMP in a program referred to as Community Utility Enhancement Services (CUES).

Located on the University of Alaska Fairbanks campus, the ARSC DSRC is leading the CUES effort. Dr. Sergei Maurits, ARSC HPC Specialist, has gathered a team from the HPCMP DSRCs nationwide to examine requirements of utility servers, perform analysis of potential utility server solutions, and work toward a set of guidelines for utility servers within the HPCMP. This is a fast-moving initiative, since utility servers are slated for testing throughout 2010, with initial implementation early in FY2011. The CUES effort is a component of the HPCMP storage initiative (SI) and will leverage several new capabilities on the HPCMP computational resources the SI is introducing.

But what is a utility server? That question is not easy to answer, because there are different and sometimes competing views on utility server functionality. For example, compute nodes might not have sufficiently large memory or external network connectivity to run interactive visualization software. Another example is pre- and postprocessing of data sets, which could require long run times but only a single CPU.

Dr. Sergei Maurits, HPC Specialist at ARSC DSRC, is leading the programwide effort to develop concepts and practices of utility servers to enhance and improve the HPCMP users' experience

Other usage examples lead to application mixes that are not typical of HPC systems, such as database software and

virtualization. Different hardware might also be a utility server component, such as graphics processing unit (GPU) accelerators or solid-state disk drives. A single utility server is unlikely to meet all of these needs, so Dr. Maurits and others are seeking to understand how different subsets of needs can be met and how utility servers can interact with mainstream batch-oriented HPC resources.

*Pingo*'s esLogin nodes are early examples of utility servers that, among other things, greatly enhance capabilities for work that otherwise would typically land on cluster login nodes. This includes compiling and serial debugging, pre- and postprocessing, and some visualization and file staging. Compared with *Pingo's* original login nodes, the new esLogin nodes provide far more memory, as well as fast connectivity to *Pingo* and to the outside world.

The esLogin nodes also help to make *Pingo* more robust to user-caused system problems. Because other *Pingo* nodes, or *Pingo's* storage subsystem, or other elements do not depend upon these nodes, users can cause node slowdowns or even crashes without impacting the rest of the system. Because of the larger memory footprint, the esLogin nodes are better equipped to handle users' nonbatch workload.

# ARSC DSRC

Front and back image of the three esLogin nodes installed on Pingo, a Cray XT5 at ARSC DSRC

The esLogin nodes supplement and in many cases replace functionality of the login nodes that originally came with *Pingo*. The original nodes were comparable with the compute nodes. Similar to the process at other DSRCs, users could choose from several login nodes to do their work. While these nodes were effective for batch job submission and monitoring, as well as compilation and some pre- and postprocessing of data, some users found them to have insufficient capacity to meet all of their needs. Occasionally, heavy uses of the default login nodes would crash the nodes or result in noticeable slow-downs for other users – such as during large-scale visualization or parallel preprocessing of input data.

The new model is for users to select from either the original login nodes or the new esLogin nodes. These have a superset of the software on the original login and compute nodes, with additional visualization software. They run a complete Linux operating system, versus compute nodes, which have a reduced OS image that is optimized for large-scale parallel computing.

Dr. Maurits and the rest of the CUES team know that esLogin nodes address only a subset of utility server needs. But many of the structural elements are wellrepresented, including high-speed access to the cluster filesystem, the ability to interact with batch jobs, capability to get dedicated interactive access to compute nodes, ability to connect back to external systems for interactive X Window sessions, large memory and a symmetric multiprocessor architecture, and software geared towards analysis and pre-/postprocessing.

The demand for such nodes to be included on new HPC systems is reinforced by the TI-10 systems set to be installed by the end of FY2010. These new Cray systems include esLogin nodes rather than the more traditional login nodes found on *Pingo*. Moving forward within CUES and the SI, the CUES team will provide guidance on new HPC systems to be dedicated to utility server functions. Interaction and overlap with existing HPC systems are intended to be as seamless as possible, while allowing users to select the best resource for their jobs.

The ARSC DSRC has a tradition of early proof-ofconcept and deployment of new technologies and services within the HPCMP. The ARSC DSRC's deep involvement in the SI and CUES and experiences with *Pingo*'s esLogin nodes will be beneficial to the HPCMP and its users as utility servers are deployed throughout the Program.

# ERDC DSRC

# U.S. Army Engineer Research and Development Center DoD Supercomputing Resource Center

## From the Director's Desk – Dr. Robert S. Maier

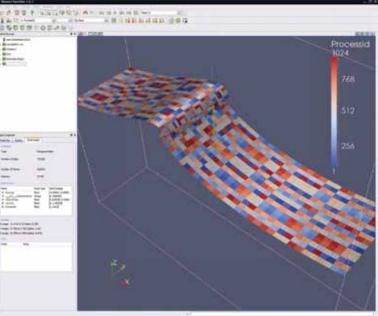

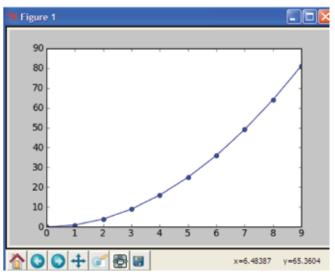

Seven years ago, then-Director John West set a goal for the ERDC DSRC to become the "big jobs" Center by ensuring end-to-end support for jobs requiring a high core count. This goal has been largely realized, within the constraints of our common HPCMP queue policies. Jay Cliburn, Lockheed-Martin Technical Lead, documents the effect in the chart below, which plots the number of jobs versus job core count. A significant number of jobs are running at higher core counts. Our 16K-core SGI Altix, a Technology Insertion 2009 (TI-09) system, is already running an unprecedented number of 2000-core jobs. Our systems are growing in size. This year, the ERDC DSRC will install a 20K-core next-generation Cray system from TI-10. We expect users will scale up their jobs accordingly, and we will do our best to enable 4000-core jobs with routine fast turnaround. Users who run at higher core counts will receive special attention and support from our staff. It is a blessing that HPC systems are growing while their cost remains relatively stable. Industry continues to follow Moore's Law, with processing speeds

Greg Rottman is leading a study of energy conservation measures for DoD data centers. His focus includes the raised floor as well as the external infrastructure. Inside the data center, opportunities for conservation

**Dr. Robert S. Maier** Director, ERDC DSRC

range from improving power distribution efficiency to more careful management of system cooling. Outside, opportunities include alternative energy sources, such as solar and geothermal. A guiding consideration in Greg's investigation is the need to work closely with system vendors to understand their roadmaps and trends in environmental requirements.

DoD provides financial assistance to the Services for energy conservation investments, through its MILCON

funding line. Indeed, there is no better time for such investments than now. As operations budgets remain constant or shrink in real terms, increasing power costs will erode our ability to support new systems. Sound financial management is essential to meeting this challenge. The recognition of costs for infrastructure support, whether incurred by the Services or by the HPCMP, will help guide our investments and our plans for the future

growing exponentially in time. According to a recent *SciDAC* article, www.scidacreview.org/0904/html/multicore.html, even power consumption is not expected to grow as fast as processing speed. Nevertheless, electricity costs represent our most significant barrier to growth, in an era of flat operations budgets.

# New Record Set on *Diamond* in Quantum Turbulence Simulations

By David Longmire, ERDC Information Technology Laboratory

Dr. George Vahala is an HPCMP Capability Application Project (CAP) enthusiast. He wrapped up his fifth CAP earlier this year and is looking forward to number six. "It's like letting loose a little boy in a candy store — with no supervision," said Dr. Vahala, Professor of Physics, College of William & Mary, Williamsburg, Virginia. "It's a wonderful, beautiful idea by the HPCMP. It's the greatest thing since chocolate!" he said.

CAPs are scheduled by the HPCMP before new systems go online for general use. Researchers compete for the opportunity of being the sole system user. The CAP gave Dr. Vahala and his team the opportunity to run their massively parallel code on an entire supercomputer for a month giving them the computing power to explore new areas of basic quantum physics research.

Dr. Vahala, joined in his research by his wife, Dr. Linda Vahala, College of Engineering & Technology, Old Dominion University, Norfolk, Virginia; Dr. Min Soe at Rogers State University; and Dr. Jeffrey Yepez, Air Force Research Laboratory, were able to set a new record in quantum turbulence simulations this year.

The CAP was conducted on the ERDC DSRC's new SGI Altix ICE 8200 named *Diamond*. "No one in quantum turbulence research has been able to run at this fine of a scale, so this is the first time that anyone has had this amount of grid resolution in a simulation," Dr. Vahala said.

"The CAP is the optimal time to use the machine. It allows us to run these huge grids; like on *Diamond*, we ran coupled Bose-Einstein condensate (BEC) states at a 4032<sup>3</sup> grid. We typically ran at 12,288 cores on *Diamond*," he said. "Dr. Vahala ran 63 of the 12,288 core jobs during the CAP. After the *Diamond* CAP was completed, Dr. Vahala ran for more than 1.5 million hours and over 40 jobs using 4096 cores, the largest the queues will now allow."

> — Bob Alter, ERDC DSRC HPC Service Center

"When you get huge grids, the amount of steps that you need scales, basically as the ratio of the grid squared; thus you have to run your simulations for much longer periods of time, and that's where the CAP comes into play. That's when you can utilize a very large number of cores with a time limit of a few weeks," Dr. Vahala said.

During the CAP, Dr. Vahala ran a total of 585 jobs and consumed 14.6 million cpu-hrs running his group's custom code called the QLG (quantum lattice gas) algorithm. The CAP runs generated more than 650 TBytes of data.

From the perspective of the DoD, the idea of the CAP is to first and foremost gain insight into challenging research problems that would lend themselves to the CAP computing environment; the Program Office also wants code that will push the system to find any problems or limitations. It is like taking a new ship on a shakedown cruise. "The DoD is very interested in the physics research data that we are getting, but it does help the systems people out. Systems people like us because we do shake it down," said Dr. Vahala.

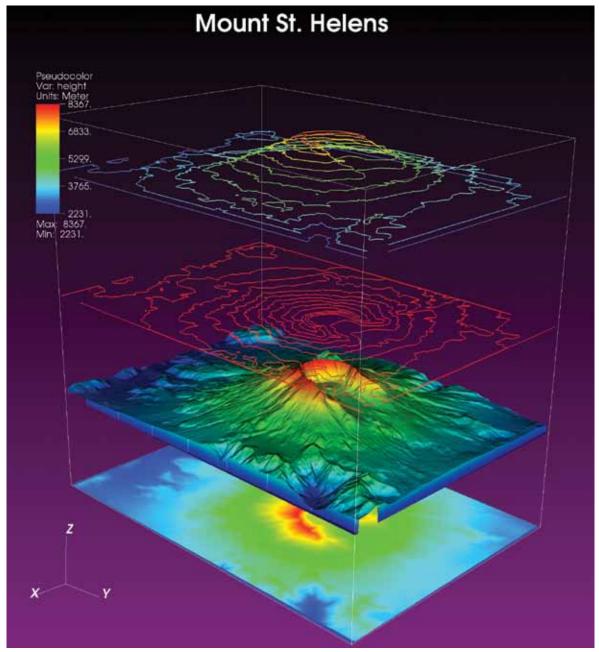

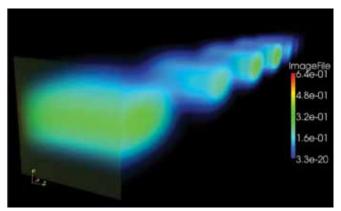

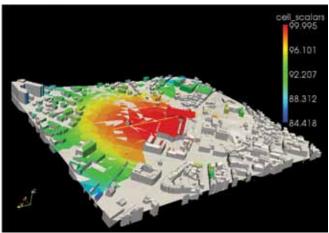

Quantum vortex simulation on a  $4032^3$  grid. The image series shows a small section of the volume data, bounded by three walls. In the first image (Time = 0), you see two of the quantum line vortices that are perpendicular to each other. The second image (Time = 10) shows the breakup of the line vortices. The third image (Time = 20) shows the small-scale vortex loops and strands. These are clearly visible utilizing the  $4032^3$  grid but would be missed in lesser resolution grid simulations. The images are from the recent CAP conducted on the ERDC DSRC's **Diamond**, an SGI Altix ICE 8200 system

"There are two aspects of this research of particular interest to the DoD. One is generating codes that will run on quantum computers when they become available, as the usual CFD codes will not run on these future quantum computers; and the second is to be able to simulate the BECs and to predict new behaviors and uses. For example, there is a great impetus to experimentally develop atom interferometry using coupled BECs. This would permit the detection of changes in the gravitational fields or magnetic fields to extreme unheard-of precisions. For example, the DoD could use these interferometers in the future to detect underground tunnels," Dr. Vahala said.

So, Dr. Vahala's code makes it possible for him and his team to look at myriad basic physics problems during a CAP. "One of the biggest things is parallelization of a code so that if you have more processors, you can use them all. The problem is that most codes will choke after about three or four thousand processors. They can't utilize more because of the communication between the processors that is needed. It is like traffic pattern flow with traffic signals that are amok — the traffic is snarled by miscued traffic signals. A perfectly parallelized code is as though the synchronization is so good that one can go from one end of town to the other end without stopping. So, you are basically limited by the algorithm. Our algorithms don't suffer that. We have always found that things speed up with more processors, and the more processors you get, the greater the grid resolution that you can run," he said.

Analyzing the more than 650 TBytes of data generated during the CAP requires special requirements. Sean Ziegeler at the Navy DSRC worked with Dr. Vahala and his group to help them visualize their data. "Sean set it up so that I could visualize the data. He got Para-View up and running on Diamond and figured out how we could dump data on these huge  $4032^3$  grids without slowing the machine down, and then we were able to use ParaView to be able to start looking at the quantum vortices. Sean Ziegeler's work was absolutely critical. It permitted parallelized viewing of the vortices during the run so that we could see if we were barking up the wrong tree or had chosen a bad parameter regime. Basically, every data point on the 4032<sup>3</sup> grid is visible so you can see the fine structure. You would never be able to see this on a 1024<sup>3</sup> grid," Dr. Vahala said.

Dr. Vahala and his group were recently published in *Physical Review Letters*. Their published paper high-lighted their research findings that directly resulted

from CAPs on *EINSTEIN* at the Navy DSRC and *Diamond* at the ERDC DSRC. "We are gaining quite a bit of insight. What we managed to do both on *EINSTEIN* and *Diamond* was pull off the energy spectrum and see the  $k^{-5/3}$  Kolmogorov Inertial Range. We were able to pull this out very nicely. It's like the classical cascades of energy. We were able to do this because we ran on such a huge grid. We also found what the spectral law was for the quantum cascade," Dr. Vahala said.

"The main thing that we found and write about in our paper was that we were able, using our quantum code and the  $4032^3$  grid, to handle the multiscale turbulence scales ranging from the classical turbulence regime right down to going into the quantum turbulence regime! This energy discovery was mainly found on the EINSTEIN CAP runs, but we did verify them on the CAP Diamond runs. Previously, other researchers had not seen this quantum cascade — partly because they introduced some extra damping terms into their simulations so as to see the classical Kolmogorov cascade. This destroyed the physics at the small scales, where the quantum cascade would live, and so they could not see the quantum cascade. The other reason is that their grids were too small anyway! Their codes hit mismatched traffic signals.

"So, for the first time the quantum cascades of energy have been identified in HPC simulation, and our research results indicate that the waves in these quantum cascades have a different structure than was theorized. We are looking further into this."

— Dr. Vahala

Classical turbulence studies are critical to the DoD and are utilized in designs for aircraft, ships, and other DoD systems. "Quantum turbulence is basically defined as vortices which are entangled. It's a spaghettitype thing," Dr. Vahala said, "which is a thousand times smaller than classical turbulence." Understanding the basic physics of the quantum vortex is the objective of Dr. Vahala's team and their data simulations generated during the recent Diamond CAP at the ERDC DSRC.

# **MHPCC DSRC**

# Maui High Performance Computing Center DoD Supercomputing Resource Center

#### From the Director's Desk – David Morton

Fiscal Year 2010 (FY10) is proving to be a year of significant growth for the MHPCC DSRC. Since the introduction in August 2009 of *Mana* (meaning power in the Hawaiian language), a new 9216-core Dell cluster, more than 500 user accounts are actively employing this HPC resource. The MHPCC DSRC has allocated more than 70,000,000 CPU hours for the HPCMP users for FY10. The MHPCC DSRC is also hosting nine high-priority HPCMP Challenge Projects with a combined allocation totaling more than 15,000,000 CPU hours.

The MHPCC DSRC is tasked to support the DoD HPCMP High Performance Computing Software Applications Institute for Space Situational Awareness (HSAI-SSA). One of nine HPCMP software institutes, the HSAI-SSA provides breakthrough capabilities by developing and transitioning HPC software applications. During the recent call for HPCMP Dedicated High Performance Computing Project Investment Award (DHPI) proposals, the AFRL DoD HSAI-SSA team proposed a system replacement for their previous DHPI systems, Hoku and Polaris. An HPCMP DHPI Award was granted. The MHPCC DSRC operations staff proposed the reuse of existing Jaws frames to support this requirement. For only eight percent of the potential awarded funds, the MHPCC DSRC was able to repurpose 640 cores of the existing Jaws system and one frame of DDN storage, upgrade the system memory to 8 GB/core, and standup the new system - Kaku (meaning barracuda in the Hawaiian language). This new Kaku HPC asset will further enable scientific and technological advances in Space Situational Awareness.

Continuous facility upgrades are ongoing to meet the growing demands of the MHPCC DSRC, which include the expansion of the Center's infrastructure and implementation of alternate green technologies (an R&D effort in advanced photovoltaic technologies). As the need for science and engineering continues to accelerate, the MHPCC DSRC continues to provide state-of-the-art technology and exceptional customer service. The MHPCC DSRC staff provide above and beyond support for special case needs. For years, the MHPCC DSRC

*David Morton* Director, MHPCC DSRC

has hosted advanced reservations, made exceptions for high-priority projects, and assisted users with codes, debugging, logins, batching, etc.

To ensure technological supremacy and to foster the flow of technology into warfighting systems, the MHPCC DSRC conducts R&D-oriented Directed Technical Tasks (DTTs) for the DoD and other government organizations. Two of the DTT Projects that the MHPCC DSRC supports recently received AFRL Directed Energy Directorate Awards. The AFRL's DoD HPCMP's HSAI-SSA received the 2009 R. Earl Good Award "For significant team contributions to the AFRL mission or image outside of AFRL and for accomplishments that have had a significant impact and enhanced the creditability of AFRL." AFRL's High Accuracy Network Determination System (HANDS) project received the 2009 International Award "For leveraged cooperative opportunities that provide mutual benefit in priority research areas that enhance and benefit the AF S&T capability."

The MHPCC DSRC continues to be a vibrant DoD organization dedicated to accelerate development and transition of the ever changing advanced defense technologies into superior warfighting capabilities.

# MHPCC DSRC

# MHPCC DSRC's Newest Supercomputer, Mana, Goes Green

#### By Marie Greene, MHPCC DSRC Deputy Director

*Mana* utilizes the latest generation of Dell PowerEdge Servers. These servers come with an extensive collection of sensors that can automatically track thermal activity helping regulate temperatures and reduce energy consumption. The sensors are designed to automatically make adjustments to help reduce energy usage. The system is also deployed with variable speed fans mounted as part of Dell's latest blade chassis subsystem. The fans automatically sense the heat generated by the components in the chassis and increase the fan speed (and thus the overall power consumption) only when the systems are active. These heat-sensing fan subsystems will also save the MHPCC DSRC thousands of dollars in energy costs over the life span of the system and reduce our overall carbon footprint as a Center.

# HPCMP Challenge Projects Have Mana's Lights Flashing

By Marie Greene, MHPCC DSRC Deputy Director

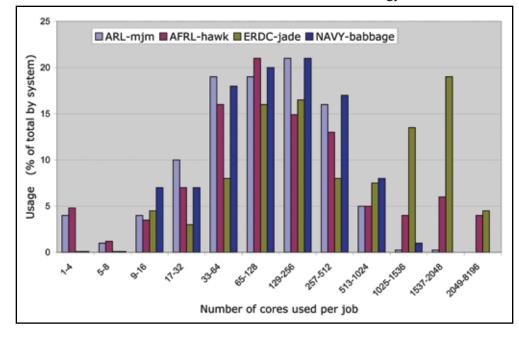

For FY10, the MHPCC DSRC is hosting nine **HPCMP** Challenge Projects allocating more than 15 million CPU hours on its newest supercomputer, Mana. Sponsors of the Challenge Projects include AFRL, the United States Air Force Academy (USAFA), the Army Research Laboratory (ARL), the Air Force SEEK EAGLE Office, and the Office of Naval Research (ONR). DoD Challenge Projects are large, computationally intensive projects. The guideline for consideration is a total computational resource requirement of at least 5 Habu-equivalent

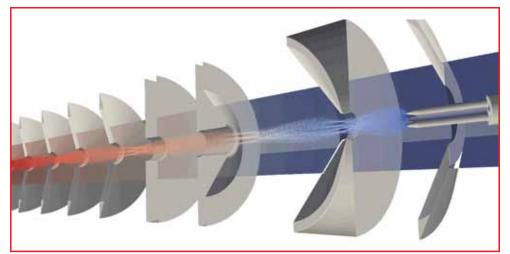

HPC modeling is used to enhance the quality of high-power lasers. The electron gun, shown in this figure, uses four 50 micron radius carbon nanotube (CNT) ropes to produce the electron beam through field emission. Four high aspect ratio CNT cathodes were used. The color of the particles represent the energy, blue being the least energetic, red being the most energetic. At the end of the cathode, the power transferred by the electron beam is 70 GW/m<sup>2</sup> (total power of 200 W and 30 microns in radius). Image courtesy of Nathaniel Lockwood, Civ USAF AFMC AFRL/RDHE

years annually, which is equivalent to approximately 2,500,000 processor-hours per year.

The FY10 HPCMP Challenge Projects that the MHPCC DSRC is currently hosting are as follows:

- Simulation of High Power Lasers (AFRL)

- Solution Virtual Prototyping of Directed Energy Weapons (AFRL)

- besign of Energetic Ionic Liquids (AFRL)

- Aero-optical Distortions in Directed Energy Applications and Their Mitigation Using Feedback Flow Control (USAFA)

- Servironmental Fate and Transport of Energetic Materials (ARL)

- Understanding and Designing Complex Ferroelectrics and Multiferroics from First Principles (ONR)

- Stability and Control Test and Evaluation Process Improvement Through Judicious Use of HPC Simulations (AF SEEK EAGLE Office)

- ✤ First Principles Studies of Ferroelectric Materials (ONR)

- Numerical Exploration of the Stable Atmospheric Boundary Level and Its Effect on Forecasting Battlefield Weather, Sensor Propagation and Diffusion, and Dispersion of Smoke and Other Agents (ARL)

#### MHPCC DSRC HPCMP DHPI Award Gives Rise to Kaku for the AMOS Site

#### By Chris Sabol, HSAI-SSA Director

The Air Force Maui Optical and Supercomputing (AMOS) site recently received an HPCMP DHPI Award to support advanced image reconstruction. A system named *Kaku* was established at the MHPCC DSRC and replaced the previous distributed center dedicated Cray XD-1 systems named *Hoku* and *Polaris*. The system was provided to the High Performance Computing Software Applications Institute for Space Situational Awareness (HSAI-SSA) software developers on December 15 and to the Maui Space Surveillance System (MSSS) users on March 11.

The MHPCC DSRC, HSAI-SSA, and MSSS are all managed through the same AFRL branch at AMOS, and all three work together to deliver unmatched ground-to-space satellite imagery to the U.S. Strategic Command and other consumers. MSSS is home to the DoD's largest optical telescope and researches advanced image reconstruction techniques such as Physically Constrained Iterative Deconvolution (PCID), an algorithm developed to remove the effects of atmospheric blurring from a series of raw images. The HSAI-SSA transformed the PCID algorithm into a robust and efficient software application (three orders of magnitude speedup over the original research code), coupled it with a user-focused, Web-hosted run management system called the Advanced SPeckle Imaging Reconstruction Environment (ASPIRE), and delivered it back to MSSS image analysts for daily use. The MHPCC DSRC is home to the HSAI-SSA, most of its software application engineers, and the HPC resources utilized for PCID/ASPIRE RDT&E. Kaku is comprised of 154 dual Woodcrest nodes (616 compute cores in total) reused from the previous MHPCC DSRC Jaws system and upgraded to 32 GB memory per node, 4 I/O nodes, and 2 login nodes. Kaku means barracuda in Hawaiian and is a skewed reference to its previous incarnation, Jaws (Jaws was actually named after one of the largest surf breaks in the world and not the fictional shark). The memory upgrades were required to support efficient operation of the PCID software with large data sets. All in all, Kaku enables a ~20x speedup in highresolution image reconstruction for AMOS and opens the door for near real-time product delivery. The Kaku team included Kathy Borelli (contractor, KJS-Consulting), Scott Spetka (contractor with Rome Laboratory, AFRL/RITB), Major David Strong (AFRL/RDSM), and Bill Stevens, Ron Viloria, Bruce Duncan, Steve Gima, and Mike McCraney (all contractors with the University of Hawaii).

## Maui Energy Improvement Initiative (MEII)

#### By Captain Joseph Dratz, MHPCC DSRC Deployed Systems Program Manager

MEII is an "American Recovery and Reinvestment Act"-funded, 15-month research effort to demonstrate the feasibility of providing photovoltaic (PV) power to Mana, MHPCC's supercomputer. The initiative will test traditional Silicon panels side by side with thirdgeneration triple-junction optical concentrator PV modules. Additionally, the effort will install 100 kW of triple junction dual-axis tracking modules to demonstrate integration with the MHPCC Data Center. This effort will provide an environmental assessment along with cost and technical data that can be fed into a longterm renewable power solution for the MHPCC DSRC.

Solar photovoltaic panel

# NAVY DSRC

# Navy DoD Supercomputing Resource Center From the Director's Desk — Tom Dunn

Providing the best computational capabilities for the Department of Defense and its high performance computing community has always been the cornerstone of the mission of the Navy DSRC. As we prepare locally for future capability enhancements, our staff continues to participate and provide leadership in numerous programwide ventures designed to broaden user access to our computational resources. These ventures include new storage infrastructure design, automated system monitoring, workload management enhancements, and leadership of automated baseline compliance-checking efforts. Having been one of the pioneer hosts of the Advance Reservation System (ARS), the Navy DSRC is now working to bring you the ARS on all of our unclassified computational systems. This system will allow users more options for running interactive and batch jobs along with current batch queuing options.

Ensuring maximum performance of our high performance computing (HPC) and storage resources is also of great importance to our team. Larger HPC platforms and more complex user jobs have led to local adjustments made to increase bandwidth to our archive servers. The Navy DSRC user outreach staff continues to look for ways to further improve their ability to assist users with challenges such as software installation and compilation, performance tool utilization, and debugging and porting applications between different architectures. Our network, security, and system administrators are vigilant in preserving system and network access and performance while anticipating future requirements both from the user community and the overall HPCMP perspective.

All of this effort rises from a simple concept: maintaining the highest possible customer

*Tom Dunn* Director, Navy DSRC

support for our users, the high performance computing community, and the Department of Defense. Customer support is not simply a goal of the Navy DSRC; rather more importantly, it is the daily driving force instilled in our entire team.

## Infrastructure Upgrades Prepare Navy DSRC for the Future

#### By Navy DSRC Staff

In early 2008, the Navy DSRC found that it would soon be welcoming *EINSTEIN*, a 12,876-core Cray XT5, and *DAVINCI*, a 5312-core IBM Power6 cluster, to its computational arsenal. Infrastructure upgrade requirements were immediately identified to accommodate the 43,800-lb *EINSTEIN* and the water-cooled *DAVINCI* in the main and secondary computer room facilities that serve the Center.

Updates to the main computer room facility required a phased approach, as the IBM Power5+ *KRAKEN* system still occupied a significant portion of the floor space there. A 73-foot wall was constructed to protect *KRAKEN* from construction debris during the 5-monthlong Phase I process. The design called for the facility to provide up to 2500 kVA of power and 640 tons of cooling (1 chiller ton is defined as 12,000 Btu/h).

The unoccupied 4650 square feet was then upgraded from a 1250-lb/ft<sup>2</sup> rated floor to a 2000-lb/ft<sup>2</sup> rated 18-inch raised floor. The former water-based fire suppression system was upgraded to the FM-200 waterless system. Equipment on this main floor, including the test system and disk racks for *EINSTEIN*, is supported by one 60-ton chiller and two 320-ton chillers, eight computer room air conditioner (CRAC) units, three 2.2 megawatt (MW) generators, and five 625 kVA Uninterruptable Power Supplies (UPSs).

In November 2009, with *KRAKEN* retired and removed from the site, work began on Phase II of the facility upgrade to enhance the remaining portion of the main computer facility. This second phase upgraded 2796 square feet of raised floor and completed the replacement of the water-based fire suppression system. The Phase II area supports an additional six CRAC units and is also supported by the chillers, generators, and UPSs that service the Phase I area.

A secondary computer room facility supports the Center's remaining computational systems including *DAVINCI*. This 8578 square foot facility houses three IBM clusters on a 2000-lb/ft<sup>2</sup> rated 30-inch raised floor. Six hundred installed tons of cooling, of which approximately 300 tons are in use at present, and 10 CRAC units provide air and water cooling. The facility is supported by emergency generators and three 1 MW UPSs.

The planned Phase II computer room upgrades have recently come to a close, leaving the Center much more prepared to accommodate future HPC hardware acquisitions. The photographs below show Phase II work in process and then completed.

Work Complete

# DAAC

# Data Analysis and Assessment Center From the Director's Desk – Dr. Michael Stephens

The DAAC is a programwide resource to assist all HPCMP users with their data visualization needs. Housed within the DAAC are several computer systems and expert staff dedicated to data visualization. The DAAC model of service is a three-tier approach. First we serve the community at-large by sharing our expertise through our Web site. This site has an ever growing number of tutorials and how-to's for a wide variety of data visualization challenges. Also at the community level, we answer users' questions specifically about visualization tools and techniques. In the second level of service, the collaborative level, users work with the DAAC staff to develop a workflow that users can then use to do their own data analysis. This often involves users sharing example data sets with the DAAC staff, thereby allowing more time to be spent exploring data analysis possibilities. In this way, both the users and DAAC grow in expertise. The users get a set of tools and knowledge

These projects usually blend together data analysis with conceptual computer animation and/or video to tell a story about the user's HPC work. These are highly polished images and movies with narration, music, etc. Think Discovery Channel.

the DAAC and how it can assist you, please visit our Web site: daac.hpc.mil.

on how to use them. DAAC gets exposure to a wide variety of data sets and visualization goals that, in turn, get shared with the entire community via our Web site. The last service level that the DAAC provides is for custom projects.

HOME | About Us | Wiki | Gallery | Software | Help

QUICK LINKS

- How can I get a viz account?

- Where can I find viz software?

- . What HPC systems support viz?

- " Where can I learn more about viz?

- " Who can help with my visualization?

- . How can I try ezViz?

New to Viz?

How can visualization benefit you? Simply put -- better insight into your data. Techniques such as <u>isosurfaces</u> and <u>streamlines</u> help you to find features in the data. Read more...

UAPHING III This Department of Definition comprehencycles is a subject to monitoring at all there. Usad there is a probability Pathic Law 16-274 (The Comprehen Frank and Annes Actor 1996).

All DoB compressions are a silence buokabulog at all thesis to each service in a single of equipmentant in definition in the definition of the single of the

UNCLASSIFIED, NON-GENSITIVE, NON-PRIVACY ACT USE ONLY

# ParaView Client-Server on Crays at the ERDC DSRC

#### By Randall Hand

Several Cray XT3, XT4, and XT5 systems are now in operation throughout the HPCMP, and several of you have migrated your codes to run in the unique Cray architecture. The three-tier architecture of the Crays (Login Nodes, Service Nodes, and Compute Nodes) causes problems for the typical client-server configurations used by visualization packages such as Kitware's ParaView. Just a subset of the problems include the following:

- Solution Library Support on Compute Nodes.

- ✤ Lack of SSH support between various tiers.

- ♥ Queuing system constraints.

The Data Analysis and Assessment Center (DAAC) has been working with Kitware on these issues and has successfully compiled and deployed ParaView on various Cray systems throughout the program. Already in use by a select few pilot users, it is now available to all of you in the Program. The instructions below will help you connect your Windows Client (with the HPCMP Kerberos Kit installed) to a ParaView server running across the Cray backend. The same procedure will work for Linux, by replacing the Putty steps with standard SSH.

#### Windows Client Connecting to Sapphire

Before we begin, here are a few notes to start. In these instructions, I refer to the ERDC DSRC Cray named *Sapphire*, specifically node "sapphire05", but it can really be any node of *Sapphire*, so long as it is consistent. The same instructions have been tested on *Jade* (ERDC) and *Pingo* (ARSC) successfully.

Also, the currently deployed version is ParaView 3.6.1, fully MPI aware but with no experimental modules enabled.

To execute ParaView on the Crays

- 1. Fire up ParaView on your client. Click on the File Menu "Connect". "Add Server".

- Give it a basic name, and select server type "Client/Server Reverse Connection". Leave the Host as Localhost and Port as 11111.

- When you click Configure, on the next screen select "Manual" and save the connection.

- Double click on the resulting connection, and ParaView should show a popup saying "Please wait while server starts.."

- 2. Pick a random number over 30,000; that will be your PORT1. Kerberize using the normal means, and then start the HPCMP putty.

- Enter a hostname, sapphire05.

- Expand the SSH area on the left, and select "Tunnels".

- Enter your selected PORT1 for the "Source Port".

- For a destination, enter "localhost:11111".

- Click the "Remote" radio button, and click Add.

- If done correctly, you should see a line read something like "R<PORT1> localhost:11111" appear.

- Save this connection if you want, then click "Open" to connect.

- 3. You should be connected to *Sapphire* now... Copy /usr/local/usp/ezViz/CNL/portfwd-sample.cfg to your home directory. Edit the two numbers in that file so that the left number is another random number over 30,000 (we will call it PORT2), and the right number is PORT1. The result should look like the following:

tcp { PORT2 { => localhost:PORT1 } }

4. Start up portfwd by executing

/usr/local/usp/ezViz/CNL/portfwd -g -c <your new config file>

It should then just sit there.

Figure 1. A 150-million cell run, visualized on 1024 processors of **Jade** (ERDC)

# DAAC

- 5. Fire up another terminal and SSH into *Sapphire* normally (any node).

- 6. Submit a queue job with the following command: aprun -n <number of nodes> /usr/ local/usp/ezViz/CNL/pvserver -rc -ch=sapphire05 -sp=PORT2

#### Linux Client Connecting to Sapphire

- 1. Fire up ParaView on your client. Click on the File Menu "Connect". "Add Server".

- Give it a basic name, and select server type "Client/Server Reverse Connection". Leave the Host as Localhost and Port as 11111.

- When you click Configure, on the next screen select "Manual" and save the connection.

- Double click on the resulting connection, and ParaView should show a popup saying "Please wait while server starts."

- 2. Pick a random number over 30,000; that will be your PORT1. Open a terminal, PKI Init, and then ssh -R PORT1:localhost:11111 username@ sapphire05.erdc.hpc.mil

- 3. You should be connected to *Sapphire* now... Copy /usr/local/usp/ezViz/CNL/portfwd-sample.cfg to your home directory. Edit the two numbers in that file so that the left number is another random number over 30,000 (we will call it PORT2), and the right number is PORT1. The result should look like tcp { PORT2 { => localhost:PORT1 } }

- 4. Start up portfwd by executing

/usr/local/usp/ezViz/CNL/portfwd -g -c

<your new config file>

It should then just sit there.

- 5. Fire up another terminal and SSH into *Sapphire* normally (any node).

- 6. Submit a queue job with the following command:

```

aprun -n <number of nodes> /usr/

local/usp/ezViz/CNL/pvserver -rc

-ch=sapphire05 -sp=PORT2

```

#### Linux Client Connecting to Jade

Jade has a slightly different configuration from Sapphire that complicates the network connectivity between the backend nodes and the client. As the backend nodes cannot directly connect to the login node via the public interface, you must take special precautions to correctly route between the two network interfaces.

1. Fire up ParaView on your client. Click on the File Menu "Connect". "Add Server".

- Give it a basic name, and select server type "Client/Server Reverse Connection". Leave the Host as Localhost and Port as 11111.

- When you click Configure, on the next screen select "Manual" and save the connection.

- Double click on the resulting connection, and ParaView should show a popup saying "Please wait while server starts.."

- Pick a random number over 30,000; that will be your PORT1. Open a terminal, PKI Init, and then ssh -R PORT1:localhost:11111 username@ jade03.erdc.hpc.mil

- 3. You should be connected to *Jade* now... Copy /usr/ local/usp/ezViz/CNL/portfwd-sample.cfg to your home directory. Edit the two numbers in that file so that the left number is another random number over 30,000 (we will call it PORT2), and the right number is PORT1. The result should look like

```

tcp { PORT2 { => localhost:PORT1 } }

```

Also edit the top line so that the "listen on" is the IP address of the "ss" interface for that login node. To get that IP address, simply execute '/sbin/if-config ss' on the node.

4. Start up portfwd by executing

/usr/local/usp/ezViz/CNL/portfwd -g -c

<your new config file>

It should then just sit there.

- 5. Fire up another terminal and SSH into *Jade* normally (any node).

- 6. Submit a queue job with the following command: aprun -n <number of nodes> /usr/local/usp/ezViz/CNL/pvserver -rc -ch=<ip address from step #3) -sp=PORT2

Unfortunately, the CNL nodes do not properly resolve hostnames, so you cannot set the "client host" (-ch) to something nice like "jade03"; you have to use the IP address of the internal interface (ss).

#### **Thoughts and Notes**

- When first testing this for accuracy and performance, use the Debug Queue with small processor counts (4 works well). You will not be able to load large data sets, but it is good enough to generate a simple Paraview Wavelet Source and benchmark.

- Users have been reporting problems attempting to submit jobs with the aprun command in the qsub script, but it works fine in Interactive when entered manually. This issue is currently under investigation.

# Graphical User Interface to Create GAMESS Input Files from Within VMD

By Michael Lasinski, Army Research Laboratory, User Productivity Enhancement, Technology, and Training (PETTT) Program, Computational Biology, Chemistry and Materials Science (CCM) Onsite

#### Problem

The Applied Systems Biology project improves biological modeling capabilities in the Army, allowing researchers to explore concepts such as engineering bacteria to be capable of cleaning up firing range toxins. A significant portion of the project's research requires the investigation of molecular systems through the use of molecular dynamics (MD) simulations. Frequently, it is also necessary to simulate part of the molecular system in extreme detail at the quantum level. Despite current high performance computing (HPC) capabilities, such detail cannot be achieved by MD simulations alone, instead requiring the combination of an MD simulation and a quantum mechanics (QM) calculation known as a quantum mechanics/molecular mechanics (QM/ MM) simulation. Typically, an MD code and a QM code are developed separately from one another. For QM/ MM simulations, this is a significant issue because both codes have to interface with one another. In fact, several difficulties stem from the lack of an efficient and userfriendly interface to set up and run a OM/MM simulation. One such difficulty with setting up a QM/MM simulation is the inability to easily select atoms from the molecular system to be included in the OM calculation.

#### Methodology

As part of the Applied Systems Biology project, Margaret Hurley, Army Research Laboratory (ARL) Weapons and Materials Research Directorate, uses the Nanotechnology Molecular Dynamics (NAMD) tool from the University of Illinois to perform MD simulations on biomolecular systems. In future portions of the project, mixed quantum/classical simulations will also be performed. While mixed quantum/classical simulation is becoming a more accepted research tool, its usage is still limited to select practitioners, and job setup and analysis is still time-intensive. Quantum-oriented graphical user interfaces (GUIs) such as Gaussview do not have the necessary graphics capabilities to work easily with large biological systems. Visual Molecular Dynamics (VMD), also from the University of Illinois, is typically used to both view such biomolecular systems and to set up MD simulations to be performed using NAMD. VMD also has some ability to create input files for QM calculations. It is not possible, however, to select atoms from a displayed molecule and then place only those atoms into an input file for a QM calculation. Furthermore, there is no ability to add to the input

file any means of dealing with the interface between the MD simulation and the QM calculation.

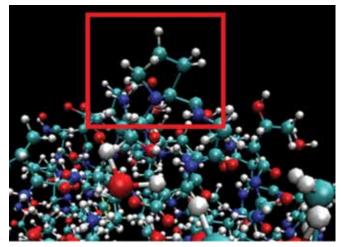

To address these issues, a GUI was written by the ARL/ DoD Supercomputing Research Center (DSRC) User Productivity Enhancement, Technology Transfer, and Training (PETTT) Program Onsite Michael Lasinski that can be added to VMD as a Tcl/Tk plugin as shown below in Figure 1. This can be done on a local desktop or on a DSRC machine where VMD is installed, such as *MJM* (the Woodcrest cluster at the ARL DSRC). With this GUI, it is now possible to select atoms by clicking on them from within VMD in order to create a GAMESS (a OM code widely available on machines such as those at the ARL DSRC) input file. The user is able to easily select individual atoms or portions of a molecule to be added to the GAMESS input file. For example, with this GUI, it is now possible to quickly add only the atoms in the red box of the molecule shown in Figure 2. (See Figure 3 for a close-up view of those specific atoms.) In addition, the GUI provides the ability to include in the GAMESS input file common OM/MM interface options such as linking hydrogen atoms and quantum capping potentials. Finally, there are additional options available to further modify the GAMESS input file such as changing the type of QM

| Gamess Inp               | at File Generator        | _ I X |

|--------------------------|--------------------------|-------|

| Elle                     | GAMESS Input File        |       |

| List Manipulati          | on:                      |       |

| Start Trace              | End Trace                |       |

| Clear List               | Create GAMESS            |       |

| Selection Crite          | ria                      |       |

| · Only Select            | ed Atoms                 |       |

| C Side Chain of Selected | s of Residues<br>Atoms   |       |

| C Residues o             | f Selected Atoms         |       |

| QM/MM Interfac           | e Options                |       |

| None                     |                          |       |

| C Hydrogen in            | place of connecting atom |       |

| C Quantum C              | apping Potential         |       |

| Coordinates Or           | ptions                   |       |

| · Cartesian              |                          |       |

| C Internal               |                          |       |

| Selection Mole           | ecute: 0                 |       |

| Selection Ator           | ns:                      |       |

| 1                        | Add to selection list    |       |

|                          | Close All                | 1     |

Figure 1. Initial GUI window

Figure 2. Protonated CPK representation of Human Deoxyhemoglobin loaded into VMD

Figure 3. Red box represents atoms selected from the molecule to be included in a quantum mechanics calculation (zoomed in from Figure 2)

calculation that is performed, changing the basis function, and using effective core potentials.

With this in place, Hurley and incoming postdoctoral fellow Scott Pendley (ARL/WMRD) will be able to apply a novel QM/MM formulation that has shown great promise on nonbiological systems, but has not been tested on enzymes. As the immediate focus of the Applied Systems Biology project is biodegradation of energetic materials, initial tests will focus on the reduction of TNT by hydrogenase. This reaction has been studied experimentally but not well enough to be completely understood. Mixed QM/MM simulations will provide sufficient detail to confirm or deny certain molecular rearrangements that have hitherto been postulated based on experimental evidence but not proven. This type of analysis is *only* possible with mixed QM/

MM methods, which have not been previously applied to this system.

#### **Users Supported**

This work supports Margaret Hurley (ARL/WMRD) by developing an interface to efficiently define the QM part of a QM/MM simulation by selecting atoms from a molecule loaded into VMD and putting them into a GAMESS input file. This GUI also provides options to handle the interface between the QM and MD part of the calculation in the GAMESS input file. By facilitating the generation of the GAMESS input file, this GUI is intended to be part of the larger effort to quickly and easily set up and run QM/MM simulations.

"This GUI will significantly speed up job submission for the QM/MM portion of the Systems Biology project and will allow my incoming postdoc to hit the ground running. Additionally, PETTT's expedited turnaround on this allowed me to focus on other portions of the work. This resulted in a briefing to ARL management with project milestones ahead of schedule."

— Margaret Hurley (ARL/WMRD)

#### **DoD Impact**

This work has wide application across the DoD by providing an efficient and user-friendly software tool that can be used to set up GAMESS input files and, ultimately, be part of a set of software tools that would better facilitate running QM/MM simulations. This tool will facilitate the use of these codes by users on ARL/ DSRC platforms to perform these calculations. As an example, this GUI will specifically help to further the stated goal of developing in-house systems biology capabilities at ARL to model biological systems. As part of the Applied Systems Biology project, these QM/ MM simulations of biological molecules will be used on a wide range of applications, the first of which will be the study of the breakdown of nitroaromatic compounds by bacteria. Nitroaromatics, which are a main component of current munitions, have toxicological and physical properties that make them an environmental hazard in areas of release, such as firing ranges and manufacturing plants. The development of bacteria that can effectively break down these compounds in situ would greatly facilitate range cleanup.

#### Acknowledgments

The authors thank the DoD High Performance Computing Modernization Program at the Army Research Laboratory for the funding of this effort.

# User Interface Toolkit (UIT) v3.1

By Wes Monceaux, Keith Rappold, and Scotty Swillie, U.S. Army Engineer Research and Development Center DoD Supercomputing Resource Center

With the programwide move to CAC for Kerberos authentication, major changes were required within the User Interface Toolkit's (UIT) architecture to accommodate the physical interaction with the common access card (CAC) reader. Basically, this move broke the UIT's anywhere, anytime, Web-only model, and a serious "rethink" had to take place to ensure this tool remained available to the High Performance Computing Modernization Program (HPCMP) users and developers.

UIT version 3.0 was the first step toward addressing CAC support for UIT applications. This version of the UIT shifted functionality from the centralized UIT Web service to the user's desktop. Along with this shift came newer capabilities, but also some drawbacks. Multitiered, multiuser Web applications were unable to utilize UIT version 3.0 because of its desktop-centric nature. UIT version 3.1 is designed to address this shortcoming.

In order to understand what has changed, a quick overview of how Version 3.0 works is needed.

#### Version 3.0 Overview

Version 3.0 requires a one-time download of ezHPC (or another interface) and the UIT that comes prepackaged with a small Web server that is run accessible only from the local system. Developers can code against this application programming interface (API) the same way that it is coded against Version 2.0 with the exception of authentication. Authentication takes place via `pkinit` or `kinit` using the DSRC Kerberos client kit, just as it is done for any other application that requires Kerberos. From that point forward, API calls by a user interface to the UIT verify that the user has a ticket and then simply uses that ticket to perform actions on the user's behalf on the HPC machines.

UIT version 3.0 requires a user to have Java Runtime version 1.5+ and the DSRC Kerberos toolkit installed for their platform.

Here's how the process works:

- Users use their SecurID card or their CAC to authenticate using the DSRC Kerberos `kinit`, `pkinit`, or similar command. Once authenticated, the ezHPC Java application running on the user's desktop then issues commands (using `ssh`) to interact with the HPC systems.

- 2. The HPC systems treat the `ssh` connections from the interface no differently than any other connections made by this user.

This version of the UIT effectively behaves just like any of the other DSRC tools (i.e., Filezilla, PuTTY, etc.) and utilizes the user's existing Kerberos tickets to interact with the HPC systems. The UIT is oblivious to how a user acquired his Kerberos ticket (CAC, HToken, or SecurID).