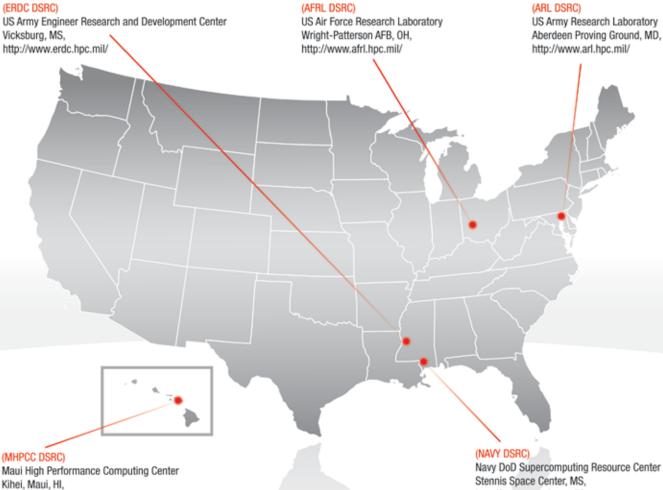

*HPC Insights* is a semiannual publication of the Department of Defense Supercomputing Resource Centers under the auspices of the High Performance Computing Modernization Program.

#### **Publication Team**

AFRL DSRC, Wright-Patterson Air Force Base, OH Gregg Anderson Chuck Abruzzino

ARL DSRC, Aberdeen Proving Ground, MD Debbie Thompson Brian Simmonds

ERDC DSRC, Vicksburg, MS Rose J. Dykes

MHPCC DSRC, Maui, HI Betty Duncan

Navy DSRC, Stennis Space Center, MS Bryan Comstock Lynn Yott

HPCMPO, Lorton, VA Denise O'Donnell Leah Glick

ASSOCIATE DIRECTOR, HPC Bobby Hunter

PUBLICATIONS MANAGER Rachelle Hintson

TECHNICAL EDITOR Emily Moynihan, ERDC

DESIGN/LAYOUT Betty Watson, ACE-IT

COVER DESIGN Data Analysis and Assessment Center

The contents of this publication are not to be used for advertising, publication, or promotional purposes. Citation of trade names does not constitute an official endorsement or approval of the use of such commercial products. Any opinions, findings, conclusions, or recommendations expressed in this publication are those of the author(s) and do not necessarily reflect the views of the DoD.

Approved for Public Release; Distribution Is Unlimited.

## Contents

| First Word                                                                                                          | 3  |

|---------------------------------------------------------------------------------------------------------------------|----|

| Special Report                                                                                                      |    |

| DoD HPCMP Computational Research and Engineering<br>Acquisition Tools and Environments (CREATE) Program             |    |

| Building Large-Scale Software in the DoD                                                                            |    |

|                                                                                                                     | /  |

| HPC At Work                                                                                                         |    |

| Numerical Flow Analysis (NFA) Simulation of a Planing Boat<br>in Waves                                              | 12 |

| Real-Time Predicition of RF Signal Attenuation Using the CPU/GI<br>Hybrid Dedicated HPC                             |    |

| Helping the HPC User                                                                                                |    |

| Code Development at the ARL DSRC – Yes you can!                                                                     | 23 |

| Portal Development for HPC at the Maui High Performance<br>Computing Center                                         | 25 |

| Centers Updates                                                                                                     |    |

| From the Director's Desk – Dr. Raju Namburu (ARL)                                                                   | 29 |

| New DSRC Facility Up and Running (ARL)                                                                              |    |

| From the Director's Desk – Jeff Graham (AFRL)                                                                       | 32 |

| Lancer – AFRL Shared-Memory Test Cluster                                                                            |    |

| From the Director's Desk – Bob Maier (ERDC)                                                                         | 34 |

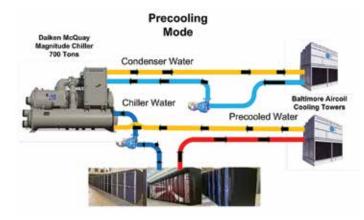

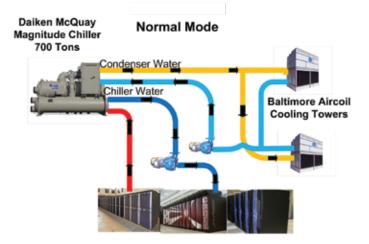

| How to Save a Cool Million Dollars                                                                                  | 35 |

| Update on Garnet – (ERDC)                                                                                           | 37 |

| From the Director's Desk – David Morton (Maui)                                                                      | 38 |

| From the Director's Desk – Tom Dunn (Navy)                                                                          | 39 |

| Improving Productivity on IBM iDataPlex Systems (Navy)                                                              | 40 |

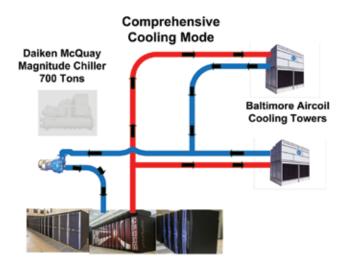

| Facility Upgrades in Support of the IBM iDataPlex Systems                                                           | 42 |

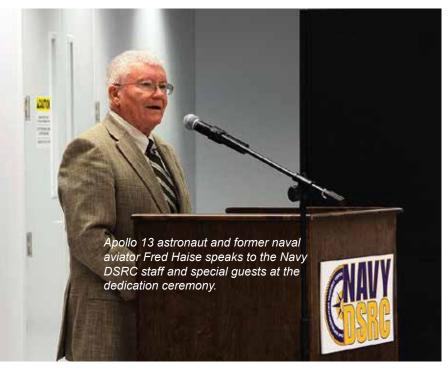

| Navy DSRC Establishes HPC System Names and Honors NASA<br>Astronaut and Former Naval Aviator Fred Haise at Ceremony | 43 |

| Interconnects                                                                                                       |    |

| Who's Your UAG Rep?                                                                                                 | 45 |

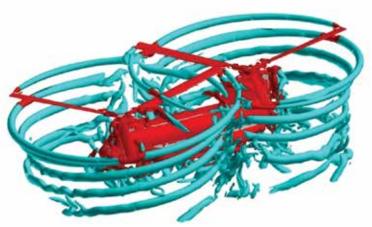

About the Cover: CREATE-AV Helios simulation of UH-60 in forward flight using adaptive wake vortex tracking. Simulation done by Mark Potsdam, AFDD. VIZ picture by Nathan Hariharan, CREATE-AV using FieldView. See story, page 7.

## **First Word**

#### By John E. West, Director, Department of Defense High Performance Computing Modernization Program Office, Vicksburg, Mississippi

In today's economic climate, I am acutely aware of the need to describe why HPC matters to our stakeholders—Congress, the Pentagon, and taxpayers. This is where your success stories play a crucial role. Distilling the power of HPC into something meaningful to American taxpayers and lawmakers can be difficult without being able to point to end products and services that demonstrate the value of HPC in their everyday lives.

Your successes send a powerful message to key decision makers: that HPC is, for many in the DoD, the tool of first resort for solving ever more complex technical problems. This message

highlights the capabilities that HPC can bring to other areas of the Department, areas that constantly strive to streamline their scientific and technical discovery processes—namely the acquisition engineering and test and evaluation communities, where HPC is not yet as fully integrated as it is in the research and development community. Our consistent message is that HPCMP resources and expertise are enabling simulations of phenomena that are only possible on HPC machines, and we must continue to invest in a robust computational capability in order to maintain our Nation's technological advantage on the battlefield.

The DoD is in a period of substantial change. I am confident that many of these changes are needed to properly position the Department for the future; however, today we are being asked to make structural changes in the way we do business. Within the HPCMP provider community, we face significant challenges in planning and budgeting, travel, contracting, security, and in our interface to the IT enterprise. HPCMP users are facing similar changes in their home organizations.

Through it all, however, we must remember that the work we are doing together—and the work we make possible for HPCMP users—is part of a much bigger picture. Together we are improving the safety and effectiveness of our Nation's fighting forces. This is a job worth doing even when our circumstances make it more difficult than we would otherwise wish.

DEPARTMENT OF DEFENSE HIGH PERFORMANCE COMPUTING MODERNIZATION PROGRAM

## DoD HPCMP Computational Research and Engineering Acquisition Tools and Environments (CREATE) Program

By Dr. Douglass Post, Chief Scientist, DoD High Performance Computing Modernization Program

he DoD HPCMP Computational Research and Engineering Acquisition Tools and Environments (CREATE) Program is a long-term program launched in FY2008 by the Office of the Secretary of Defense. The objective is to develop and deploy multiphysics-based computational engineering software that, when used in conjunction with increasingly capable high performance computing systems, accurately predicts the performance of naval, air, and radio frequency antenna weapons systems. These tools are designed to enable trade space optimization of new and retrofit designs and to avoid costly (time and money) design flaws and rework. The ultimate goal of CREATE is to catalyze a revolution in weapons system design, and development methodology from reliance on building and testing physical prototypes to virtual prototype design and evaluation, followed by physical prototype validation for the DoD Government and industry research, engineering, and acquisition communities.

The CREATE Program is developing nine individual software applications. The CREATE Air Vehicles project consists of DaVinci-a conceptual design tool; and Kestrel and HELIOS (Helicopter Overset Simulations)-high-fidelity, full-vehicle, multiphysics analysis tools for fixed-wing and rotary-wing aircraft, respectively. The CREATE Ships project consists of the Rapid Ship Design Environment (RSDE)-or conceptual design of ships; NavyFOAM-or prediction of ship hydrodynamic performance; Navy Enhanced Sierra Mechanics (NESM)-for analysis of ship shock and shock damage; and the Integrated Hydro Design Environment (IHDE)-to facilitate use of naval design tools. The CREATE Radio Frequency Antenna project application, SENTRi, is a tool for analyzing and optimizing the performance of RF antennas integrated with DoD weapon platforms. A fourth project, Meshing and Geometry (MG), consists of Capstone, a set of tools for generating the geometries and meshes needed by the other CREATE tools. This collection of tools provides an integrated design and analysis capability that can be applied at all stages of the acquisition process, from requirements definition and conceptual design through sustainment and platform modernization. They are already being used to analyze existing DoD weapon systems and to design new systems. Led by the HPCMP,

Helios calculation of interaction of vortices from rotor-tips on the CH-47.

this software is being developed by multi-institutional teams of Government and contractor personnel located at military laboratories and facilities with the relevant technical expertise and customer communities for each application area. For instance, NESM is being developed by a group at the Carderock Naval Surface Warfare Center that has the lead for shock vulnerability of naval vessels.

Each year, the CREATE teams release a new version of each software application with increased capability to meet technical and usability requirements of its customer base. For CREATE AV, DaVinci 1.0 provided an initial capability to construct a new airframe model from "parts" that can be combined into an integrated airframe model for analysis. This capability is being used to assess candidate designs for the next-generation Air Force cargo aircraft, among other applications. Kestrel v3.0 enables simulations with two or more bodies in relative motion with control surfaces, providing the ability to calculate store separation, together with the ability to achieve stated accuracy and parallel scaling goals. Kestrel is being used to assess flight worthiness and performance for a number of DoD existing and planned aircraft, including six UAV candidate systems. HELIOS v3.0 enables general multirotor and fuselage modeling for a complete rotorcraft and an automated adaptive mesh refinement scheme that enables accurate tracking of the vortices to study rotor and fuselage interactions. This capability is being used to assess the proposed CH-47 rotor retrofit that is designed to provide an additional 2000 pounds of lift for hover operation.

For CREATE Ships, RSDE is being used for a pilot

project for the DoD Engineered Resilient Systems Program to demonstrate the utility of design optimization of naval vessels. NESM v1.1 provides the capability to conduct a virtual "Full Ship Shock Trial" to analyze the vulnerability of equipment function in a naval vessel to underwater explosions. This capability is being validated for the Full Ship Shock Trial alternative for the CVN-78, the Navy's new class of aircraft carriers. NavyFOAM v3.0 provides the capability to assess ship hull resistance and maneuvering capability. An ongoing application is the design of the bow planes and maneuvering empennage for the Ohio Replacement Submarine, the Navy's new Ballistic Missile Launch Submarine. IHDE added an enhanced ability to analyze bare hull resistance, seaway loads, and seakeeping with a large number of simultaneous analyses. These capabilities are being used to analyze many different ships, including the DDG-51 Flight III bow bulb modification, the Medium Affordable Surface Combatant (MASC), and the Green Arctic Patrol Vessel (GAPV).

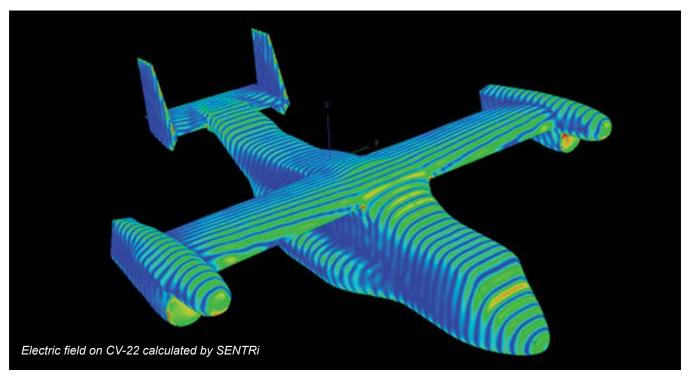

The latest version of SENTRi, v3.0, provides much faster algorithms for electromagnetic analysis that allow assessment of larger and more complex antennas and platforms and the ability to handle anisotropic and continuously varying materials. SENTRi can calculate the time-varying electric field patterns on full-sized aircraft such as the CV-22 Osprey Tilt-rotor and Apache helicopter, and it is being applied to other DoD weapon systems as well. Capstone v3.0 provides automated, near-body volume meshing with boundary layers, improved capability to generate unstructured surface meshes, and other improvements. It is being used to provide meshes for next-generation Air Force cargo plane designs generated with DaVinci and for other applications. Group (JACG), composed of the commanders of the AF Life Cycle Management Center, NAVAIR, and Army Aviation, formed a Tri-Service Integrated Project Team to oversee the USC and to develop a plan for the DoD Aviation community to fund the USC once the HPCMP seed money has been expended. The Air Force Arnold Engineering and Development Complex is hosting and setting up the USC. There is strong interest in the CREATE tools by the US Defense industry. Motivated by the promise of the CREATE software and other physics-based models, the NDIA has established a conference series on Physics-based Modeling for U.S. Defense that features the CREATE software. A number of major Defense industries (Boeing, Bell Helicopter, Raytheon...) are beginning to use the CREATE tools and are showing interest in adopting them into their product development workflow.

Increasingly restrictive computer security access requirements are reducing the ability of DoD scientists and engineers to access high performance computing resources (including the CREATE tools) from their workplaces. A likely endpoint of the present process is that all DoD computer users will have access to only Microsoft Office and a web browser, precluding use of scientific and engineering tools and limiting the use of the HPCMP computers. To allow engineers and scientists access to the HPCMP resources, the HPCMP and CREATE have begun developing a "portal" capability that provides secure access through a modern browser. The initial pilot project is being executed by the Maui DSRC and CREATE. It involves developing a portal that allows a remote user with only a browser to set up, run, and analyze Kestrel problems through a browser. Success with Kestrel is being extended to all the CREATE tools and will be available to facilitate the use of other applications on the HPCMP computers.

The CREATE customer and user communities

continue to grow. Over 50 programs are now DoD using the CREATE tools to address acquisition program issues. Over 500 licenses for CREATE software tools have been issued (although not all of these are active). The growth of users has led to the need to support them. The HPCMP has provided funding to seed the establishment of a User Support Consortium (USC) by the DoD Aviation community. The Joint Aeronautical Commander's

Adoption of the use of CREATE software by the acquisition engineering community is essential for success. In addition to ensuring user support, the CREATE team is working with ERDC, the DoD, and the Defense industry to address intellectual property and technology transfer issues that need to be resolved to ensure adoption of the CREATE tools while protecting the sensitive information in the tools through export control mechanisms and other means. Among the options being explored are Cooperative Research and Development Agreements (CRADAs) with individual industries, Broad Area Announcements (BAAs), and other contract mechanisms. In addition, to facilitate adoption of the tools, CREATE is supporting use of nonsensitive versions of their CREATE tools by the U.S. Military Academies and by academic groups, such as naval architecture and aeronautical engineering departments of a number of major universities, as part of their course curricula.

The CREATE Program is approaching the midpoint of the planned development schedule. While the original CREATE software engineering strategies have been successful, the team has evaluated the effectiveness and is recasting them to improve the CREATE development process. Key process areas that have emerged as crucial are ensuring the sufficient focus on the development team, meeting customer needs, employing technically mature component technologies, identifying and employing successful agile development methodologies, and gathering requirements in an effective manner. While the features and technical capability of the software will continue to be improving, a major focus during the second half of the CREATE program will be improving usability, including scaling and improved user interfaces and user access, and increasing the focus on verification and validation together with the addition of methods for quantifying uncertainties.

CREATE staff have continued to receive national and international recognition and awards from professional societies and from the Services. These include two AIAA and an SNAME Fellow appointments, the National Academy of Sciences Gibbs Brothers Medal for Naval Architecture, the ASNE 2011 Gold Medal, the IDC HPC Innovation Excellence 2012 Award (given to the HPCMP for work done by a CREATE staff member), and The Technical Cooperation Program (TTCP) 2012 Scientific Achievement Award, as well as numerous internal DoD and Service awards.

The CREATE Program is successfully developing and deploying software with the new features needed by the DoD aircraft, Naval, and RF engineering communites. Customer growth is strong, both in terms of users and programs. CREATE software is already contributing to the analysis and design of important DoD systems, such as the CH-47 rotor-blade retrofit, the Ohio replacement submarine, the CVN-78 shock test, the NAVAIR UAV flight certification, the AF next-generation cargo plane, and many other systems. Progress is continuing in all areas, including user support and access, Intellectual Property and deployment issues, and Software Engineering.

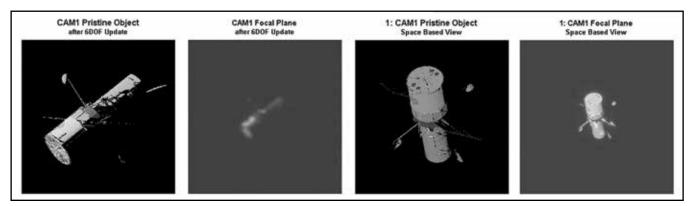

## HPC Tools Clear the Path for Unmanned Air Vehicles

By Theresa Shafer, Naval Air Systems Command (NAVAIR 4.3.2.1), Applied Aerodynamic and Store Separation Branch

#### Problem

To respond to requests for proposal (RFPs) for unmanned aircraft vehicle (UAV) systems, companies need to demonstrate the performance of their proposed UAV systems. Also, Navy aircraft require air worthiness certification, which normally requires data from wind tunnel tests, flight tests, or empirical methods. Traditional aircraft design programs use computational fluid dynamics (CFD) analysis, wind tunnel testing, and flight testing to obtain flight clearances. However, small UAV development programs do not have the resources to obtain extensive databases needed to support full flight clearance decisions.

#### How

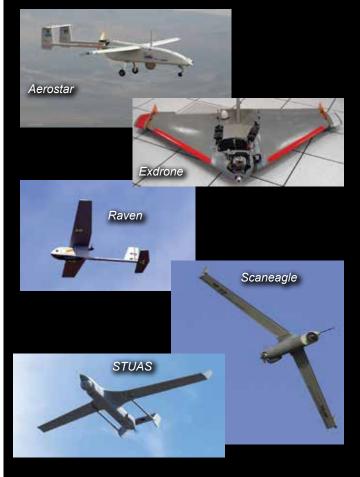

Shadow Ops used CFD to create a database that can be used in flight clearance decisions, which enabled small UAV programs to obtain flight clearance certifications. The CREATE-Air Vehicles (AV) created a standard, streamlined, validated process using enhanced methods to support the small UAV flight clearances using computational methods, which was applied to the small UAVs Exdrone and Aerostar. For the Exdrone UAV, the computationally-based engineering (CBE) model was created from 2D drawings, and six configurations/grids and 205 data points were generated and completed. In 2009, an original aerodynamic database for Aerostar was created. The engineers created the 3D CBE model by using a coordinate measuring machine and a flight vehicle. Nine configurations/grids were generated, and 176 data points were created.

#### Impact

The data generated through computational methods as part of the Aerostar UAV effort helped to mitigate risk in the flight certification process by providing engineers with sound data with which to make more informed air worthiness assessments. The small UAV program office (PMA-263) has since relied on this process to gain clearances for the Raven, Aerostar, and Exdrone vehicles. Databases in support of clearances for the SCANEAGLE and STUAS vehicles are currently in progress using the same process. Unbiased aerodynamic performance data were provided to the PMA-263 for aerodynamic assessment of vehicles enabling flight envelope definitions based on accurate, engineering data. Flight clearances have been defined based on the data created by the CREATE-AV program.

AeroVironment RQ-11 Raven is a small hand-launched remote-controlled unmanned aerial vehicle (or SUAV).

PMA-263 is NAVAIR's program office for Navy and Marine Corps Small Tactical Unmanned Aircraft System.

Using the established process of CFD analysis, differences in forces and moments on the Aerostar vehicle because of the presence of the antennas was calculated in a timely manner and communicated with the performance and flight dynamic subject matter experts. The data directly affected the flight clearance decision allowing these subject matter experts to make a decision on the flight clearance for Aerostar with these antennas. The same approach has been used two to three times a year for Aerostar with geometric modifications and was used on the Raven vehicle to provide decision makers with a flight dynamic and performance evaluation capability throughout its life cycle that was not possible prior to using these CFD tools.

Additional impacts include the small UAV flight clearance support. CFD was used to assess the aerodynamic effects of adding two minipods to Aerostar in two loading configurations. More than 90 runs were completed, and data and recommendations were supplied to the technical area experts in four days. CFD was also used to examine the aerodynamic effects of adding four antennas in various configurations. Sixty runs were completed; and data was supplied to technical area experts in less than 1 week, which was used to directly support the Greenbox flight clearance.

#### **Metrics**

There was an improvement in time and cost from the Exdrone to the Aerostar UAV:

• Exdrone UAV: 4 months to complete and cost about \$80k, much less than the cost of a full wind tunnel test.

• Aerostar UAV: 6 weeks to complete and cost about \$30k, reducing the time and cost because of the lessons learned from the Exdrone assessment.

Flight certifications for small UAVs have a tight turnaround time (2 to 6 weeks). For a single UAV, the ShadowOps team completed about 200 separate runs that use 128 to 512 processors each. In 2009, about 1 million computational hours were used for this project. In 2010, 1.8 million computational hours were used. For the Aerostar Greenbox clearance (adding antennas to Aerostar), 4 grids, 60 computational solutions, and postprocessed data were completed in 1 week. Completing this many runs in such a short time could not have been accomplished without HPCMP resources.

#### Who Did the Work

The program office (PMA-263) that supports the CREATE-AV ShadowOps has continued to fund the effort for small UAV clearance support since the Exdrone and Aerostar projects were completed. Dr. Theresa Shafer, a NAVAIR 4.3 aerospace engineer on loan, led the UAV effort.

#### What Tools Were Used

The Kestrel high-fidelity modeling tool for fixedwing aircraft CFD, structural mechanics, propulsion, and control was used. The systems that were used to process the data were the following HPCMP resources: *Diamond*, *Harold*, *Mana*, *Hawk*, *Falcon*, *MJM*, *Raptor*, and *Garnet*.

# What Is CREATE: A New Approach for Reducing Weapon System Acquisition Time and Cost

As a part of the HPCMP, the Computational Research and Engineering Acquisition Tools and Environments (CREATE) program is developing sophisticated multiphysics-based computational engineering design and analysis software tools. This brings the fruits of many years of research to bear on current and future engineering challenges. Used with the HPCMP high performance computers, these tools can identify and help eliminate design defects and integration problems much earlier in weapon systems design and test processes, before major schedule and budget commitments are made, resulting in reduced acquisition time and cost. CREATE addresses the dual need for (1) development and optimization of integrated conceptual

#### **Other Impacted Systems**

The methodology was applied to obtain flight certification data for the following small UAV systems being assessed by NAVAIR:

designs and (2) high-fidelity, detailed design analysis of DoD aircraft, ship, and radio-frequency antenna weapon systems. Engineers can use the tools from the initial stages of acquisition through sustainment. CREATE tools allow engineers to rely more heavily on computational prototypes that can be constructed less expensively and much earlier in the acquisition process than experimental prototypes, well before metal is cut. Testing can then focus on validating mature designs and on investigating the basic physical phenomena that determine system performance. The CREATE tools are being developed and deployed by teams hosted by Service research and development, engineering, and acquisition organizations (e.g., SEEK EAGLE Eglin Air Force Base and Naval Surface Warfare Center Carderock). While funded primarily by the HPCMP, the Services are investing time and energy introducing the new tools and processes into individual projects and planning for long-term support. The tools are already being used by over 50 DoD programs.

## Building Large-Scale Software in the DoD

*By Maria Murphy, MHPCC DSRC Sr. Applications Engineer, and Chris Atwood, CREATE, High Performance Computing Modernization Program Office*

few years ago, the CREATE development team was looking for the collaborative functions of GitHub, SourceForge, Forge.mil, or Google Code—but with secure authentication and access to thousands of cores. The extended team now includes several dozen developers and hundreds of users spanning five time zones. More formally, several studies note that while collaboration is not the sole independent variable determining the outcome of projects, it is crucial in addressing the key project factors: scoping mission, retaining stakeholder support, capturing requirements, scheduling, engaging clients, completing technical tasks, monitoring and controlling projects, troubleshooting and ultimately the client accepting the resulting software product (Atwood *et al.* 2010).

Software development teams have evolved to this highly-collaborative development model over the past few years. This evolution is exemplified by the growth in open-source efforts, which have resulted in a wide range of applications, including Linux, Apache, MySQL, and Android. These community efforts have driven the widespread adoption of tools and practices that enable collaboration with distributed members, each member potentially originating from differing organizations, geographies, or backgrounds. The distributed nature of these software product efforts is similar to the distributed Computational Research and Engineering Acquisition Tools and Environments (CREATE) software program (Post 2008). However, a significant complicating factor for DoD code arises from the security policies required for the development and deployment of International Traffic in Arms Regulations (ITAR) materials, which address issues of national interest. These necessary security elements include authentication, authorization, network access controls, server hosting constraints, and user client system privileges, each of which may vary by institution, management, and physical site.

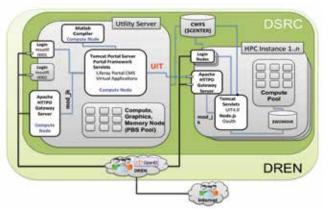

This article summarizes the effort to support successful project practices while minimizing interruption to developers, which has resulted in the implementation of collaboration systems configured at <u>http://create.</u> <u>hpc.mil</u> to transparently facilitate, document, and institutionalize (1) communication among all the key roles in the project and (2) support and feature requests from the user community and from stakeholders from DoD Programs.

#### **CREATE Program**

The CREATE program is designed to improve the DoD acquisition process (AP) by developing and deploying three sets of advanced computational engineering design tools. Acquisition programs use these tools for the design of military air vehicles, ships, and RFantennas. The military air vehicle (AV) design project will develop a design optimization tool that can simulate unsteady, separated flow, initially for individual aircraft components and ultimately for an entire aircraft. The military ship (SH) design project will develop and deploy accurate, physics-based models, for Navy vessels, that address three key capabilities: ship-shock response, hydrodynamics, and design space exploration for concept design. The RF-antenna design project will build an efficient electromagnetic design code that incorporates modern physics and computational algorithms for high performance computers. Since all three of these projects depend on discretization, a fourth project has been refactored, one focused on modeling, meshing and geometry (MG). This new generation of computational design tools will enable acquisition system engineers to rapidly produce optimized designs for complete systems and to make better design decisions than has been possible with prior design tools.

#### **CREATE Community Services – Governance Model**

In support of these software project efforts, a CREATE Collaboration Council (CCC) has been formed whose members include each of the CREATE Project Managers, members of the HPCMPO staff representing the DoD Supercomputing Resource Centers (DSRCs), and the Defense Research and Engineering Network (DREN). The CCC provides recommendations, with risks and mitigations, to the CREATE Program Office (PO) for Go/No-Go decisions. The CCC mission is to impact DoD Acquisition Programs by recommending collaboration tools and program processes for the benefit of CREATE software developers and of the AP engineering user community. Pursuant to the Program software engineering practices, the Council aims to provide easily-accessible, productive, and secure means of sharing practices across the software lifecycle; including code configuration, unit testing, continuous integration methodologies, techniques, Application Programming Interfaces (API) sharing, issues and defects tracking, software manuals, video tutorials, training material to the AP workforce, and software support. From the recommendations of the CCC and with the approval of the PO, a collection of services has been hosted to support the application development lifecycle.

#### **Application Development Lifecycle Services**

#### **Code Repository**

One key difference between a research project and a sustainable application is the ability of multiple developers to edit, build, test, and debug via a shared code repository. Software version control enables collaborating on a specific version of the code or tracking the revision history for debugging and code release purposes. The key requirements for the configuration management software include (1) developer ease-of-use with multiple languages, (2) wide use in commercial or open-source projects to enable fast support as well as longevity of the software, and (3) integration with issue-tracking software for CREATE product sustaining use. For the current iteration, the development teams chose Subversion (SVN) because of its widespread use in both commercial and open-source projects, enabling rapid support and relative assurance of continued development with limited cost-impact. In addition, SVN is extensible via plug-ins available for many developer environments and languages and is accessible with GIT clients as well as with continuous integration and issue tracking systems.

#### **Issue Tracking**

A second key element of project management is tracking issue status in a way that incurs minimal interruption in the primary deliverables of the team. Issue-tracking systems are crucial for recording defects, tasks, requirements, and feature requests in a manner that sets expectations for due dates and action item ownership. Tracking systems also passively build a knowledge repository for the project, providing rolebased context for project issues, in contrast to mail, which is associated with individual personnel at that particular time. In addition, issue tracking can be used to establish a feature list for future releases, as well as link to dependent issues, a code repository, and the user community forum. With such systems, metrics, such as the amount of code addition, defect time-to-fix, and feature time-to-implement, can be queried without interrupting the development, testing, or customer teams. Hence, this tool is useful for evaluating the health of the product from a full-lifecycle perspective, from concept, through development, to customer feedback.

Atlassian JIRA was chosen as the issue tracker based on its SVN integration, source-code availability, visibility scoping, robust database for backup and queries, packaging for hosting in a secured domain,

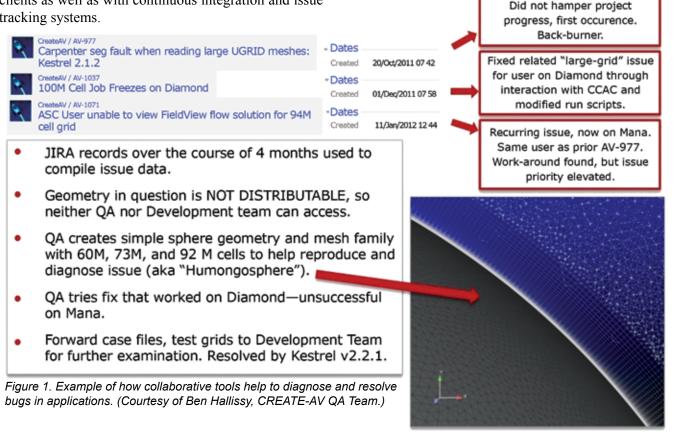

and issue submission and modification capabilities via web or email. Current CREATE use of JIRA contains approximately 6000 assigned issues across 12 projects, which are in states ranging from open to resolved to closed. Figure 1 depicts a scenario in which the issue tracker was used to compile data on a recurring problem involving a large grid. Successive iterations between the CREATE-AV Quality Assurance (QA) and development teams and the users helped to enable a bug fix in the next release.

#### **Discussion Forum and Wiki**

In modern software development efforts, it is common for users to form a Community of Practice (COP) for self-help and for engagement with the development team in a scalable manner. Our DoD community is no different in this respect, with a goal of the CREATE project to enable DoD and defense industry engineers access to the integrated capability of HPC software and hardware, allowing them to solve problems that cannot be solved by other means. The purpose of the CREATE web-based user community discussion forum is to scale the knowledge base of the CREATE Community via a searchable archive, which organically grows with each version of the codes released. The forum mechanism offers the advantage of passively capturing project institutional knowledge, information which might otherwise be lost in personto-person mail and, hence, inaccessible to benefit future community members. In addition, development team experts moderate the forum, providing responses that are generally useful to the entire community and reducing the burden of duplicate responses to similar issues that users experience. As the COP grows, the forum enables the user community to help each other so that the development team does not have to respond individually to each question that arises in the use of the code. Although there are many forum software applications available, the forum software phpBB was selected based on the requirements of configurability for separable access by users and developers, healthy community support, search functionality, availability of integration with issue tracker and wiki, daily digests, low initial and recurring costs, and server maintenance ease. The currently implemented discussion forum

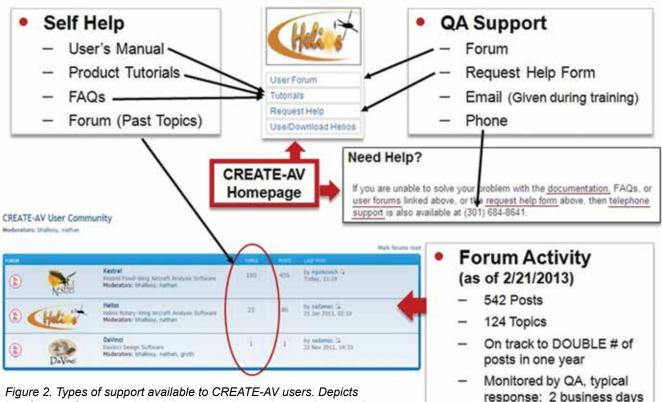

## Types of Support Available

Figure 2. Types of support available to CREATE-AV users. Depicts interfaces to forums, technical documentation, and manuals and help. (Courtesy of Ben Hallissy, CREATE-AV QA Team.)

contains approximately 3200 posts across 650 threads, primarily oriented at troubleshooting discussions within the development team members. The threads of discussions may culminate in an action item, for which a cross-posting link is generally provided to the issue tracker or wiki.

Separately from the forum, a wiki functions as a structured space for users to access tutorials, to download software releases, and to submit formal help requests. Confluence offers delegated access control mechanism and versioning features, which allow authors to manage distribution of their content (e.g., meeting minutes, project documents, and technical references) as well as to maintain a history of modifications. Figure 2 summarizes the types of support available from the forum and wiki collaboration services to users of one of the CREATE software products.

#### Server and Network Architecture

The CREATE Community server applications, consisting of issue tracking, code management, document repositories, and forum and wiki services, are hosted individually on separate web servers. This configuration minimizes interruptions to all other services should one server require maintenance or upgrades, and provides protection against application dependency and port conflicts. Application servers are deployed on virtual machines residing on two physical servers and are managed by KVM software. All systems run Red Hat Enterprise Linux 5 64-bit distribution.

A majority of the CREATE Community web server applications consists of components commonly found in the LAMP (Linux, Apache, MySQL, PHP/ Perl) architecture. All Apache web applications are configured securely and provide HTTPS encryption. The CREATE servers exist on a separate subnet within DREN, and a combination of information security technologies protect them. User management is based on a system that can quickly grant or revoke specific privileges, with service access based on roles assigned to an individual user. In this manner, CREATE can accommodate various access levels required for both developers and end-users without incurring significant administrative overhead.

All services are accessed by the user via the CREATE Community site, <u>http://create.hpc.mil</u>, which serves as the mechanism for licensing, single sign-on (SSO) authentication, and access control to available applications. The portal interface provides a consistent and intuitive method for accessing common services, as well as a customized content area, for each design project.

#### **DSRC Application Deploy and Buildmastering**

The AP subject matter expert community is generally quite busy. Therefore, it may benefit from a quick means to evaluate the CREATE tools and to then begin using them if the tools are deemed useful. Hence, it is beneficial to have CREATE software pre-installed, preconfigured, and verified on their systems. The CREATE Community team has engaged with the HPCMP Baseline Configuration Team to enable this capability on the DSRC systems (Graham and Kevorkian 2013). This enables users to avoid the tedious and error-prone process of building, installing, configuring, testing, and administering the software prior to their productive duties of using the software for their AP task. Once the engineer is authorized to access the ITAR material, use of the software is straightforward, typically starting with the use of the tutorial sample test cases provided at the CREATE Home locations on the DSRC systems.

Although the CREATE teams generally provide their software on the DSRC systems, they must build, test, and execute the CREATE software on a range of systems to satisfy the user requirements for access to the software on local workgroup clusters as well as on the DSRC systems. Since the CREATE-AV project will require that released versions of the code are supported on the then-current interpreter, development compilers, and runtime libraries, builds of the software are required for the targeted user-base. The Buildmaster performs these builds as part of the release engineering process of porting the CREATE-AV codes from development platform to the release-supported platforms, including DSRC systems, workgroup clusters, client workstations, and connecting networks. The Buildmaster collaborates closely with development teams on identification, scoping, and tracking of issues found during the build process and also implements automated build reporting, including performance measures across the supported platforms and identifying opportunities for refactoring common runtime libraries for CREATE-AV codes. In addition, the Buildmaster influences the DSRCs on implementation of common software configurations with the goal of improving the acquisition engineering usage of the software.

#### Software Integration and Test

To integrate components from disparate teams into one application, for example CREATE-RF SENTRi integration of CREATE-MG Capstone SDK, the combinatorics of components, build tools, operating systems, and libraries become difficult to manage. To enable this type of integration, test systems for CREATE software and hardware must support multiple product platforms (Windows, OSX, Linux) and their variants (e.g., Vista and 7 for Windows, CentOS and other Linux distributions). Providing permanent and continuous access to each supported OS platform is critical for product testing, robustness, and stability. As the combination of supported platforms increases, the ability to purchase sufficient hardware becomes challenging. To fulfill these requirements, the most costeffective method of addressing platform availability is virtualization. A single virtual machine could host each required platform and handle the build, test, and integration activities for that operating system. Multiple projects could use any virtual machine (VM), which reduces duplication of commonly supported platforms. The Common Build Server system will deploy upwards of 12 platforms running on individual VMs.

#### **HPC Portal**

The user-friendly HPC Portal, <u>http://www.portal.</u> <u>hpc.mil</u>, which allows users with varying levels of HPC experience to process jobs using nothing more than a web browser, provides access to the CREATE community tools from its interface. This integration offers users the convenience of access to tutorials, examples, documentation, and help without workflow interruptions. For example, a user who has submitted a job via the Portal has an issue with divergence because of the input mesh files. Without switching context, he can refer to the CREATE forum to research the problem or to submit a formal help request via the wiki.

#### Software Adoption and User Analytics

To successfully transition the CREATE technology to the stakeholder community, establishing familiarity and confidence in the successful use of the software tools by the users is key. A measure of success for the CREATE software is the adoption and use of the application. Ultimately, an acquisition program that successfully leverages the software is a good measure of value, with the AP engaging CREATE via its engineering members in the community. This engagement can be measured via forum activity, support requests, or software use. To gain better quantification of the CREATE user base, the team has begun gathering user analytics. Because of security concerns, accumulating site data statistics requires a self-hosted analytics solution. Piwik is an open-source alternative to software-as-aservice (SaaS) solutions, such as Google Analytics, and provides complete privacy and control of the data that is collected. Piwik has been integrated with CREATE wiki and forums to compile web traffic data (such as visitors' geolocation, sources, activity, and technical capabilities) and to generate user engagement reports.

#### Conclusion

The collaborative community software services that support the CREATE efforts have, in part, led to successful adoption of HPC computational physics software in several Air Force, Navy, and Army Programs. The community services have enabled feedback directly from the stakeholder and users to the CREATE software teams, creating quick response capability. Over the past few years, the community site has grown to 447 authorized users, 160 of whom have accessed the site in February 2013. Ultimately, the value of these services will be measured by impact to DoD programs and their engineering users, users whom we are engaging with the CREATE Community site.

#### References

Atwood, C. A., S. A. Adamec, M.D Murphy, D. E. Post, and L. Handley-Blair. 2010. Collaborative Software Development of Scalable DoD Computational Engineering. In 2010 DoD High Performance Computing Modernization Program Users Group Conference (HPCMP UGC), 14–17 June, Schaumburg, IL.

Graham, J. and A. K. Kevorkian. 2013. *HPCMP DSRC Baseline Configuration*. <u>http://www.ccac.hpc.mil/consolidated/bc/team.php</u>.

Post, D. E. for the CREATE Team. 2008. A new DoD initiative: the Computational Research and Engineering Acquisition Tools and Environments (CREATE) Program. *Journal of Physics: Conference Series* 125(1).

## Numerical Flow Analysis (NFA) Simulation of a Planing Boat in Waves

By Thomas O'Shea, Dr. Douglas Dommermuth, Dr. Kyle Brucker, Lucas Rhymes, and Donald Wyatt, NFA Simulations, NFA Simulations, SAIC; Dr. Michael Stephens, Chris Lewis, Richard Walters, Miguel Valenciano, and Michael Wissmann, Flow Visualization, Data Analysis and Assessment Center (DAAC); and John Levesque, Parallel Computing Guidance, SAIC

#### HPC Resources: Cray XE6 (Raptor), AFRL DSRC; Cray XE6 (Garnet), ERDC DSRC

recent collaboration between DAAC; US Army Engineer and Research and Development Center; and the NFA simulation team, SAIC, has allowed high-fidelity numerical simulations of a planing craft in a seaway to be realistically rendered. High-quality visualizations allow researchers to gain insight into the complex multiscale physics involved.

#### Motivation

Personnel aboard high-speed planing boats can experience substantial accelerations in a seaway. They can be injured when the shock loads that cause these accelerations are extreme. These shock loads also wreak havoc on the boat's structural members. Time spent on heavy seas can significantly shorten a planing boat's overall operational lifetime.

Quantifying the extreme pressures and forces on a planing hull can help guide the design process but can also be difficult to accomplish. Computational Fluid Dynamics (CFD) offers one path, but the problem is especially challenging. Pressures on a planing boat hull are concentrated at the spray root and can move significantly with only slight changes in vessel orientation. This makes the force-mass balance sensitive to any errors in the simulation. High spatial resolution is needed to capture the short extent of the spray root and also any small features on the hull (steps, chines, etc.). The addition of a seaway necessitates high temporal resolution to capture wave slamming events, which can happen over extremely short periods of time.

Leveraging Department of Defense (DoD) high performance computing (HPC) resources, simulations were completed with the high spatial and temporal resolution necessary for accurate results. These resources are used efficiently because of recent advances in NFA input, output, and core algorithms. Guiding these improvements were scaling studies performed across multiple HPC resources. Insights gained should make even larger, more sophisticated calculations possible.

#### Approach

NFA solves the Navier-Stokes equations utilizing a Cartesian grid cut-cell formulation with a second-order accurate, volume-of-fluid (VOF) interface-capturing technique to model the unsteady flow of air and water around moving bodies. The Cartesian grid cut-cell method avoids a complex body-fitted grid generation process, which enables the rapid analysis of new hull geometries. Turbulence is modeled with an implicit subgrid-scale model that is built into the treatment of the convective terms in the momentum equations (Rottman *et al.* 2010). A domain decomposition method is used to distribute portions of the solution domain over a large number of processors. Detailed descriptions of the numerical algorithm and of its implementation, using Fortran 2003 and the Message Passing Interface (MPI), on distributed memory HPC platforms are provided in Dommermuth et al. (2007), O'Shea et al. (2008), and Brucker et al. (2011).

#### **Planing Craft Simulation**

Simulations of a high-speed planing boat accelerating from rest to a constant forward speed in head seas were performed using NFA. The boat is permitted to have four degrees-of-freedom, including sway, heave, roll, and pitch. Integration of the pressure on the wetted surface provides a means to understand the shock loads the crew will experience. Analysis of these loads will facilitate the design of vessels that will provide a smoother ride without adversely affecting craft performance. Visualization of the locations and spatial extent of the high pressure regions on the hull aids in the analysis of the fatigue life of structural members.

The planing boat in this simulation has a length, *L*, of 62.3 ft (19 m) and was traveling at a velocity, *U*, of 40 knots (20.6 m/s), equating to a Froude number of 1.5, defined as  $Fr = U/\sqrt{gL}$  where *g* is the acceleration of gravity. The domain has a length, width, and depth of 4.3 (81.7 m), 2.0 (38 m), and 1.8 (34.75 m) boat lengths, respectively. The number of cells in x, y, and z was 1536, 1024, and 512, respectively, resulting in 805 million cells in the total simulation. Spacing near the body was 0.0018 *L*, or 1.3 in. (3.4 cm), necessitating a nondimensional time-step of  $6.24 \times 10^{-4}$  ( $6.77 \times 10^{-4}$  seconds.) The simulation was run for 70,000 time-steps, or 44 body lengths, which corresponds to about 30 wave impacts.

The research was completed on the Cray® (Cray Inc.) XE6 located at the Air Force Research Laboratory (AFRL) DoD Supercomputing Resource Center

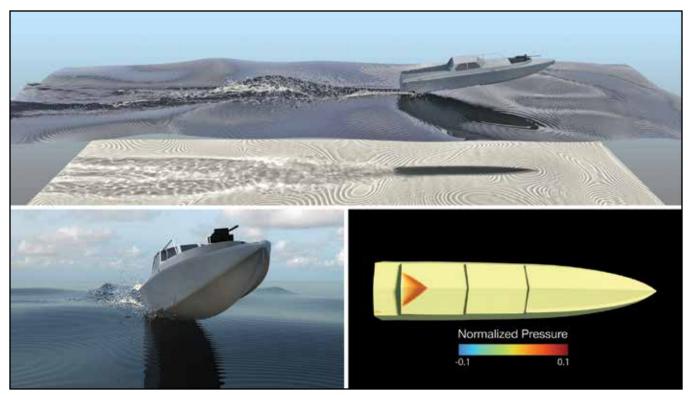

Figure 1. Planing boat motion off crest of a wave and resultant surface pressures on hull.

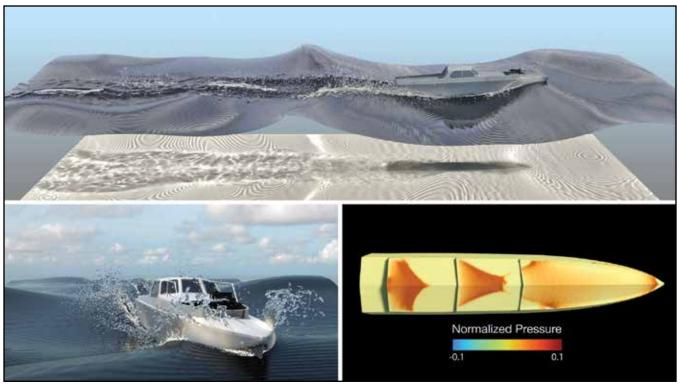

Figure 2. Planing boat motion slamming into waves and resultant surface pressures on hull.

(DSRC). The 805 million grid cells of this simulation were distributed over 3072 cores and run for 190 wall-clock hours.

Figure 1 illustrates the planing vessel launching off a wave. The highest pressures occur along the spray root, evident as the sharp interface between minimal pressure, yellow on the color bar, and high pressure, highlighted in red. At this instant, the entire craft is supported by the small wetted surface area with high pressure. Within a few seconds in a seaway, the portion of the boat in contact with the free surface can either be a small area at the stern, as in Figure 1, or can be distributed over the extent of the craft when the boat slams back down between waves, as shown in Figure 2, or various alternate configurations. Slamming of the craft back down into a wave produces the greatest amount of wave breaking and spray generation. Throughout the simulation, waves break at the rooster tail behind the boat. Wave breaking also occurs along the edges of the Kelvin wake. Ambient waves form spilling breakers toward the back of the computational domain. Videos of this simulation, as well as those of other NFA simulations, can be seen at <u>http://www.</u> youtube.com/WaveAnimations.

#### Visualization

Isosurfaces output during the simulation were provided to the Data Analysis and Assessment Center (DAAC) in two sets of Visualization Toolkit (VTK) geometry files. The first set represented the free water surface and had on the order of 5.5 million triangles per isosurface. The second set represented the boat's geometry and was provided with a scalar pressure value per node.

From these two sets of data files, the DAAC produced three types of animations: several realistic perspective views, a bottom view showing normalized pressures experienced by the boat hull, and a caustics study of light through the turbulent wake.

The realistic animations were accomplished by ray tracing the scene with reflection and transparency attributes applied to the water using Adobe 3D Studio Max commercial rendering software. A special rendering model of the boat was developed by applying rich texture maps to one of the simulation boat isosurfaces. Each frame was rendered via 3D Studio Max scripts that performed the following sequence:

```

for each frame {

import texture mapped boat file;

import next simulation boat file;

import next simulation water surface file;

orient texture mapped boat to the

simulation boat position;

delete simulation boat from scene, (leaving

only the correctly oriented textured

boat);

render the scene;

```

The bottom view was shown simultaneously with the realistic view. Dramatic slamming of the boat from the realistic views could be quantified by the color mapped pressure displayed on the boat hull, as shown in Figures 1 and 2.

Finally, a visualization employing caustics was produced by the DAAC team. Caustics are the collection of light rays that are reflected or refracted through a curved surface. Light rays were ray cast through the wake and projected onto a surface located some distance under the bottom of the boat. This visualization technique results in light and dark bands on the bottom surface that provides more information about the structure of the turbulence of the wake.

#### **Assessment of Numerical Predictions**

Past efforts to verify the use of NFA for the prediction of the hydrodynamic forces and moments associated with planing craft, through detailed comparison with available experimental data, are described in O'Shea et al. (2012), Fu et al. (2012), and Brucker et al. (2012).

Under the direction of Dr. Craig Merrill at the Naval Surface Warfare Center, Carderock Division (NSWCCD), NFA was delivered and installed at the Ship Engineering and Analysis Technology (SEATech) Center in January 2012, where it is currently being used to research stepped planing boat design. As part of that process, predictions made using NFA are being compared with ongoing towing tank experiments.

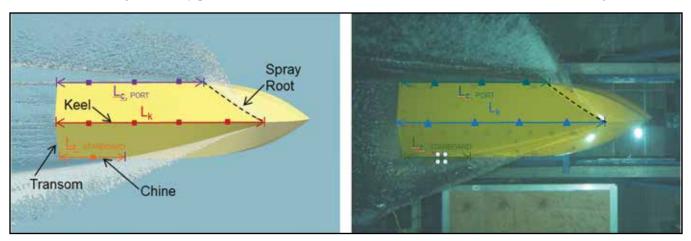

One example of this continual experimental verification includes comparison with a forced-roll experiment of a prismatic planing hull conducted by the United States Naval Academy (USNA), described in Judge (2012). This assessment illustrates the capability of NFA to accurately model the complex multiphase flow associated with high Froude number flows associated with planing craft. Experimental underwater photographs were compared with NFA simulations of a planing hull, with steady forward speed at fixed sinkage and trim, at a series of roll angles.

This simulation was run with a width of two boat lengths, or 10 ft (3 m), and a depth of one boat length, or 5 ft (1.5 m), corresponding to a smaller domain than the towing tank dimensions in order to cluster cells near the body without stretching the grid too heavily. The number of cells in x, y, and z was 1280, 896, and 448, respectively, resulting in 514 million cells in the total simulation. Spacing near the body was 0.0009 *L* or 0.054 in., necessitating a nondimensional time-step of 0.00023. Simulations were run for 13,000 time-steps, or three body lengths that were sufficient to reach steady state, on *Garnet*, a Cray® (Cray Inc.) XE6 at the U.S. Army Engineer Research and Development Center (ERDC) DSRC, and took approximately 24 hours to complete using 576 cores.

The generation of the spray sheet is correctly predicted; the spray edge matches well to experiments.

}

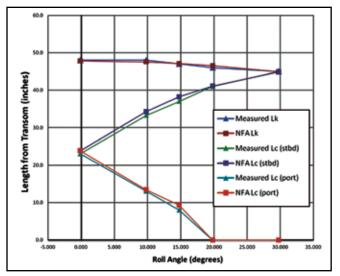

As the model rolls over, the flow over the chine initially separates cleanly; but at 20 degrees and higher, the flow wraps around the chine and wets the side of the model. The NFA simulations exhibit this behavior. Figure 3 shows comparisons with experimental photos taken at 10 degrees of roll. The spray root line, and thus wetted surface area, are demonstrated to agree. NFA appears to model the instabilities in the spray sheet breakup reasonably well. The bottom of the model was painted with a ruler, and the length along the keel  $(L_{\nu})$  and along both the port and starboard chines  $(L_{a})$  from the transom to the spray root was estimated from the underwater pictures by the experimentalist. Figure 4 presents the comparison of the same values extracted from the NFA results. The resulting agreement is excellent throughout the range of roll angles, indicating that the wetted surface area is being accurately predicted.

The parallel embedded isosurface output capability allows data to be extracted efficiently, facilitating much higher temporal resolution for quantities of interest while also massively reducing the amount of data output and postprocessing time. Strain on the mass storage and archival storage systems is therefore reduced while the quality of both the visualizations and scientific/ engineering data is improved.

Isosurfaces for the planing boat simulations were output every 5 time-steps, corresponding to a dimensional sampling frequency of 295 Hz; and the entire data field (three velocity components, pressure, and volume fraction) was output every 20 time-steps (75 Hz) to permit analysis of turbulence, air entrainment, and spray formation. Each save of the entire data field requires 6.2 GB of storage, totaling 21.7 TB for the entire run. Extracting isosurfaces

Figure 3. Planing boat with 10 degrees of roll, with NFA simulation results on left and experimental photograph on right. View is from underneath craft. Line colors and marker shapes correspond to quantitative values shown in Figure 4.

#### **HPC Considerations**

#### **Dynamic Output Control**

The flow visualization of large datasets, including rendering of isosurfaces and volumetric data, is difficult. NFA has developed many output tools that have proven to be invaluable in the analysis of large CFD datasets. Variables in the data can be extracted in the form of lines, planes, isosurfaces, or full fields. The ability to change these output types, values, and locations on the fly, as a simulation is running, is a valuable innovation that allows rapid isolation of important features in the data, allowing more efficient research. Data storage requirements, queue time, computer hours, and calendar time are all saved by being able to redirect focus and to change data analysis and visualization techniques dynamically as desired.

Figure 4. Comparison of spray sheet formation and contact line measurements.

reduces this by a factor of 92, allowing for the sampling frequency of the extraction to be increased by a factor of 4 while only requiring 3.8 TB of storage for the run. All output files are written in binary format, to reduce size, in a format requiring no postprocessing. Output files can be directly opened with visualization software based on the Visualization Tool Kit (VTK), such as the freely available Department of Energy (DOE) funded ParaViewTM (Kit, Inc.) software.

#### **User Efficiency**

Identical NFA code, analysis tools, and infrastructure can be run on desktops running Windows, Linux, or Mac-OSX and on many HPC platforms including Cray® (Cray, Inc.) XT3, XT4, XT5, and XE6, SGI Altix, or IBM P5, and P6, and iDataPlex. Small runs (10+ million grid points) are completed in minutes, medium runs (100+ million grid points) in hours, and large runs (1+ billion grid points) in a day. Portability, coupled with an intuitive GUI and a dynamic output capability, makes NFA an easy-to-use, robust, and efficient platform from the end-user perspective.

#### Solver Efficiency

Efficiently solving a complex elliptic problem, like the pressure field in an incompressible flow simulation, with billions of unknowns is a difficult problem. Poor conditioning because of a 1000:1 density jump across the air/water interface and an embedded irregular boundary condition on the ship hull make the problem even more difficult. NFA uses a multigrid solver, without which small simulations would be difficult and large parallel simulations intractable. Much effort has been put into the NFA's multigrid algorithm, as it accounts for 60 to 80 percent of the simulation time.

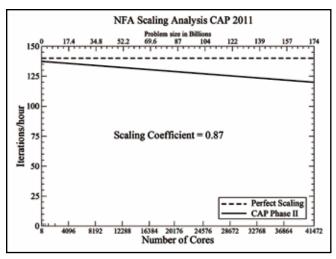

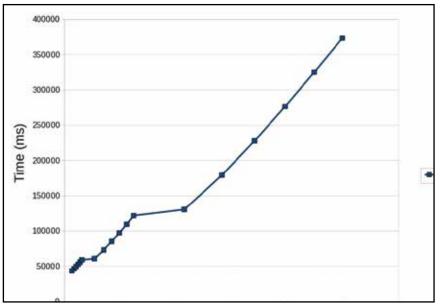

Under the 2010 Capability Application Project (CAP) program, scaling studies including iterations per hour and weak scaling efficiency of NFA were completed. A significant improvement to the scaling, at large core counts (>1024), was made as a result of replacing the one-sided remote memory access (RMA) MPI communication model, which required barriers, with a two-sided nonblocking send/receive communication model completed by John Levesque and the Cray Supercomputing Center of Excellence. Figure 5 shows the scaling results of simulations with fixed blocks of  $256 \times 128 \times 128$  grid cells per core distributed over numbers of cores ranging between 8, resulting in 33.6 million grid points, and 41,472, resulting in 174 billion grid points. These simulations require 1.9 GB of memory per core, which is near the 2-GB-per-core hardware limit. The largest simulation demonstrates

Figure 5. Iterations per hour achieved with 256 × 128 × 128 grid points per core (maximum based on 2 GB/core available memory).

the full ability of the AFRL DSRC Cray® (Cray, Inc.) XE6, *Raptor*, using nearly all of the available memory and all of the available cores concurrently to simulate a complex free-surface flow with 174 billion grid points. Notably, NFA only requires 2 GB of memory per core, or less, and has no increased memory requirements when expanding the problem size by adding additional compute cores.

The weak scaling coefficient of 0.87 bodes well for NFA to scale out to hundreds of thousands of cores and to one trillion or more grid points. Testing on such large problems should become possible once the DoD completes consolidation of the three Cray® (Cray, Inc.) XE6 machines (*Chugach, Raptor*, and *Garnet*), as 151,040 cores will become available on a single machine.

#### Conclusions

Advanced visualization techniques have brought an NFA simulation of a planing boat, with a simulated wavefield, to life by realistically rendering the hydrodynamic output. The detailed multiphase flow associated with the formation of the spray sheet and free-surface turbulence of planing boat hydrodynamics at high Froude number has been verified through comparison with experimental data. This demonstrates that NFA can successfully model these complex fluid flows and the resulting impact on vessel motion and stability.

Efforts to reduce memory usage and improve scaling performance allow runs to be spread across greater numbers of processors to drastically reduce run time. Because of efficient, dynamic output, NFA is able to reduce disk utilization to manageable levels even when simulations involve billions of grid cells. NFA is now well positioned to serve as a useful tool for evaluating novel planing hull-forms and to solve even larger, more sophisticated hydrodynamic problems.

#### Acknowledgments

This work is supported in part by a grant of computer time from the Department of Defense High Performance Computing Modernization Program (HPCMP) (<u>http://www.hpcmo.hpc.mil/</u>). The numerical simulations were performed on the Cray XE6 platforms, located at the ERDC and AFRL DSRCs.

NFA research and development has been sponsored over the years by SAIC Internal Research and Development (IR&D) funding, the Office of Naval Research (ONR), and the Naval Surface Warfare Center, Carderock Division (NSWCCD). The program managers are Dr. Patrick Purtell, Dr. Steven Russell, Dr. Paul Hess III, Dr. Ronald Joslin, Dr. Bob Brizzolara, Dr.Tom Drake, and Dr. Thomas Fu.

#### References

Brucker, K. A., T. T. O'Shea, and D. G. Dommermuth, J. Levesque. 2011. Numerical Flow Analysis Capability Application Project 2010. In *Proceedings of the 21st Department of Defense High Performance Computing Modernization Program's User Group Conference, Portland, OR.*

Brucker, K. A., T. T. O'Shea, and D. G. Dommermuth. 2012. Numerical Flow Analysis of Planing Boats. In *Proceedings of the 22<sup>nd</sup> Department of Defense High Performance Computing Modernization Program's User Group Conference*. IEEE.

Dommermuth, D. G., T. T. O'Shea, D. C. Wyatt, T. Ratcliffe, G. D. Weymouth, K. L. Hendrikson, D. K. Yue, M. Sussman, P. Adams, and M. Valenciano. 2007. An Application of Cartesian-Grid and Volume-of-Fluid Methods to Numerical Ship Hydrodynamics. In *Proceedings of the* 9<sup>th</sup> International Conference on Numerical Ship Hydrodynamics, Ann Arbor, MI.

Fu, T. C., T. T. O'Shea, C. Q. Judge, D. G. Dommermuth, K. A. Brucker, and D. C. Wyatt. 2012. A Detailed Assessment of Numerical Flow Analysis (NFA) to Predict the Hydrodynamics of a Deep-V Planing Hull. In *Proceedings of the 29<sup>th</sup> Symposium on Naval Hydrodynamics, Gothenburg, Sweden*.

Judge, C. Q. 2012. Static and Dynamic Forces and Wetted Lengths for a Planing Hull Model Forced in Roll. In *Proceedings of the 3<sup>rd</sup> Chesapeake Power Boat Symposium, Annapolis, MD*.

O'Shea, T. T., K. A. Brucker, D. C. Wyatt, D. G. Dommermuth, and T. C. Fu. 2012. A Detailed Validation of Numerical Flow Analysis (NFA) to Predict the Hydrodynamics of a Deep-V Planing Hull. In *Proceedings of the 3<sup>rd</sup> Chesapeake Power Boat Symposium, Annapolis, MD*.

O'Shea, T. T., K. A. Brucker, D. G. Dommermuth, and D. C. Wyatt. 2008. A Numerical Formulation for Simulating Free-Surface Hydrodynamics. In *Proceedings of the 27<sup>th</sup> Symposium on Naval Hydrodynamics, Seoul, Korea.*

Rottman, J. W., K. A. Brucker, D. G. Dommermuth, and D. Broutman. 2010. Parameterization of the Internal Wave Field Generated by a Submarine and its Turbulent Wake in a Uniformly Stratified Fluid. In *Proceedings of the 28th Symposium on Naval Hydrodynamics, Pasadena, CA.*

## Real-Time Prediction of RF Signal Attenuation Using the CPU/GPU Hybrid Dedicated HPC Project Initiative at ARL

By Brian J. Henz, U.S. Army Research Laboratory (ARL), Aberdeen Proving Ground, Maryland; Evens Jean, Secure Mission Solutions, North Charleston, South Carolina; David Richie, Brown Deer Technology, Forest Hill, Maryland; Song Jun Park, ARL; James A. Ross, Dynamics Research Corporation, Reston, Virginia; and Dale R. Shiers, ARL

The scale and complexity of mobile ad-hoc networks (MANETs) used by the Department of Defense (DoD) are unique and continuously increasing, particularly within the Army, creating a mobile fighting force. The military is rapidly becoming a network-centric force, with substantial access to sensor derived surveillance information, as well as to an increasingly complicated application layer running over many different devices. Each layer introduces significant advantages to the Warfighter but also brings in new dependencies and new risks from the rapid change in configurations of the MANETs that provide network access across the battlefield. Largescale testing, evaluation, and analysis of MANET platforms is an expensive vet necessary undertaking requiring extensive study of the quality of mobile radio transmissions that are affected by many environmental factors such as terrain, foliage, and weather conditions, to cite a few. Simulation and emulation tools have been developed to support such studies of MANET, with emulation holding great promise in limiting the amount of live experimentation required for platform development. Emulation provides for hardware-inthe-loop (HIL) testing and analysis where the physical medium is replaced by a virtual environment, and a physical or simulated radio can be used with real applications. At the physical layer, the interaction between devices is governed by the RF propagation characteristics of the environment.

Independent of the approach, the accurate simulation or emulation of mobile radios requires the computation of RF propagation path loss in order to predict connectivity and signal interference. RF propagation models play an essential role in the planning, analysis, and optimization of radio networks (Schmitz and Weng 2006; Rick and Mathar 2007; Michea and Komatitsch 2010). For instance, coverage and interference estimates of network configurations are based on field strength predictions; routing is also highly dependent upon computed path loss data. RF propagation path loss predictions for MANET emulation has traditionally relied on either off-line link analysis using various models including high-fidelity finite difference time domain (FDTD) and ray tracing methods or real-time calculations with stochastic models (Kaplan et al. 2009; Nitsche and Fuhrmann 2011). MANET emulation with HIL capabilities requires that the path loss data be computed and provided to the emulation environment in real-time despite the computational complexity of proposed path loss algorithms. A more realistic physical layer for MANET emulations and simulations can be achieved through the use of high performance computing (HPC) resources and graphics processing units (GPUs) to provide the floating point performance required to compute the RF propagation path loss algorithms in real-time. To that end, the Mobile Network Modeling Institute (MNMI), headed by the U.S. Army Research Laboratory (ARL), was established in 2007 to exploit HPC resources through the development of computational software for MANET analysis. The goal of the MNMI is to enable the DoD to design, test, and optimize networks at sufficient levels of fidelity and with sufficient speed to understand the behavior of network technologies in the full range of conditions under which they will be deployed.

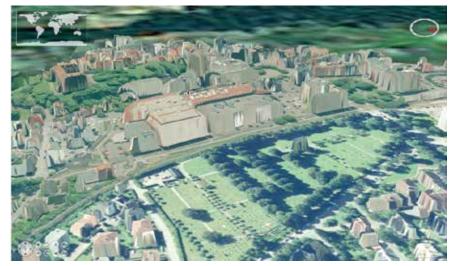

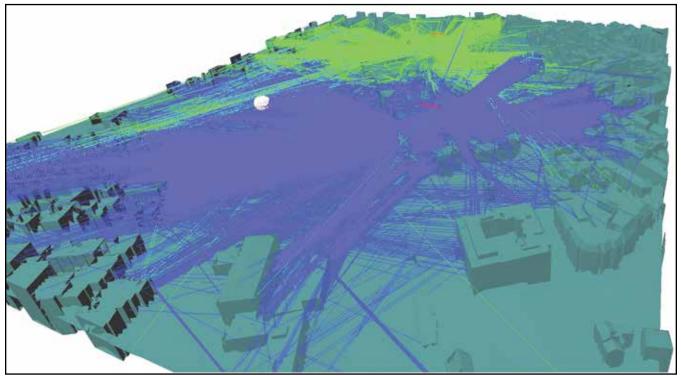

Operational goals of the MNMI include the development of scalable computational modeling tools for simulations and emulations, the ability to understand *a priori* the performance of proposed radio waveforms in the field, and the optimization of the network for U.S. Army warfighters. In this article, we present an overview of our work in computing the RF path loss of mobile radios utilizing a dedicated HPC system and the ray tracing algorithm (Nitsche and Fuhrmann 2011; Bertoni 1999) in urban environments, such as depicted in Figure 1.

The results presented here stem from an ARL effort to develop a framework for large-scale MANET emulations (e.g., up to 5000 emulated devices) through the use of the Extendable Mobile Ad-hoc Network Emulator (EMANE) from DRS (formerly Cengen Labs) (Galgano et al. 2012). The ARL framework will serve as a test bed for research, development, and evaluation of network algorithms, applications, and devices. The framework makes extensive use of HPC resources and GPUs to mitigate the computational complexity of RF path loss algorithms that are typically  $O(n^2)$  where *n* is the number of transmitter/receiver device pairs.

The available methods for computing RF path loss require a large number of floating point operations (FLOPs), necessitating a high FLOP rate for real-time path loss predictions. We have investigated the development of three algorithms for use on GPUs: the irregular terrain model, the transmission line matrix method, and the ray tracing method. The Irregular Terrain Model (ITM) is well suited for use with large-scale emulations of 1000s of devices but fares poorly in urban environments (Longley and Rice 1968). The Transmission Line Matrix (TLM)

Figure 1. Polygon representation of Tonsberg, Norway.

algorithm is targeted towards pico-cell scenarios within buildings or in relatively localized urban environments (Christopoulos 1995). TLM relies on the relationship between electromagnetic field quantities and voltage and current on transmission lines. The algorithm is computationally expensive,  $O(n^3)$ . The ray method is used primarily for small-scale to large-scale urban environments and is at the center of our current discussion.

The use of GPUs has been identified as a solution to provide raw FLOP performance (Song and Akoglu 2011) for real-time path loss computations. Initially developed for rapid rasterization, GPUs tend to exceed the performance of CPU architectures for raw FLOP rates, hence their use in our work. We further relied on Standard CL (STDCL) (Brown Deer Technology 2012), which leverages OpenCLTM (Khronos Group 2012) to present a more efficient and simplified interface designed for the complexities of heterogeneous computing platforms (GPUs/CPUs) and HPC applications.

Our efforts have recently focused on developing a ray tracing algorithm optimized for GPUs and HPCs for use in real-time MANET emulations. Previous work in the field has focused on efficient methods for computing the propagation path loss using ray tracing (Liang and Bertoni 1998) and also porting of the ray tracing algorithm to GPUs. Minimizing the path loss computation time through algorithm development and GPU optimizations is of prime importance. Within the study of RF propagation, ray tracing is a technique by which a large set of rays emanating from a transmitter are launched in all directions of interest. The rays are then traced to study the attenuation of the signal as they undergo reflection, diffraction, scattering, and refraction through their interactions with objects in the environment.

The virtual environment used in this study is a polygon-based 3D representation of the town of Tonsberg, Norway (Figure 1). The model consists of 68,356 triangles stored on the GPU. For each transmitter in the system, we rely on the GPGPU cores to trace the paths of individual rays that have been generated through initialization, reflection, and diffraction. The rays are generated based on user-specified values  $n_a$ and  $n_{\alpha}$  that represents the number of  $\theta$  and  $\varphi$  angle partitions of a unit sphere surrounding the transmitter. The product  $n_{\theta} \cdot n_{\phi}$  is the number of initially generated rays. The path of the reflected rays from interaction with the model is computed based on the laws of reflection in light propagation. Computing the RF path loss seen at a particular point in the environment in the presence of reflected rays takes into account the unfolded path length of the rays, as well as the number of reflections that the rays have undergone. As ray tracing exhibits a high degree of parallelism through the uncoupled transmission of individual rays, by increasing the number of processing cores available, the computation time is reduced proportionally. The path of a ray depends upon the interaction of the ray with the model's polygons. Figure 2 showcases the path of individual rays from two transmitters to one receiver through the environment.

Performance of the emulation test bed system is tightly coupled with the ability to efficiently compute the signal attenuation. With the ITM algorithm, we investigated the effect of changing the amount of work performed per kernel execution. We varied the stripe size from 1024 to 2048 point-to-point calculations and noticed an improvement of roughly 10 percent across different GPUs as shown in Table 1. When the block size is increased to 4096, the improvement is not as drastic, leading us to conclude that increasing the block size further would yield diminishing returns.

| Table 1. Performance for AMD and NVIDIA GPUs as afunction of block size in terms of rthe number of point-to-point paths evaluated per kernel execution |            |          |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------|--|--|

| Processor                                                                                                                                              | Block Size | Time (s) |  |  |

| ATI Radeon HD 5870                                                                                                                                     | 1024       | 83       |  |  |

| ATI Radeon HD 5870                                                                                                                                     | 2048       | 75       |  |  |

| ATI Radeon HD 5870                                                                                                                                     | 4096       | 72       |  |  |

| AMD Radeon HD 6970                                                                                                                                     | 1024       | 65       |  |  |

| AMD Radeon HD 6970                                                                                                                                     | 2048       | 58       |  |  |

| AMD Radeon HD 6970                                                                                                                                     | 4096       | 55       |  |  |

| NVIDIA Tesla C2070                                                                                                                                     | 1024       | 42       |  |  |

| NVIDIA Tesla C2070                                                                                                                                     | 2048       | 40       |  |  |

| NVIDIA Tesla C2070                                                                                                                                     | 4096       | 39       |  |  |

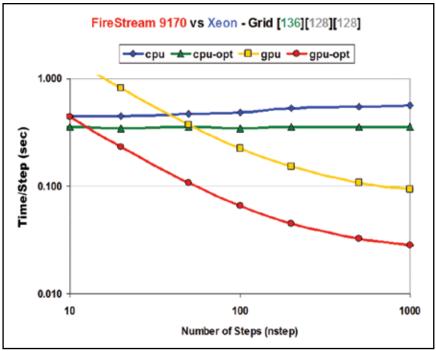

For comparison, the TLM is well suited for computation on GPU architectures. In this case, the biggest bottleneck is expected to be data transfer across the PCIe bus, which is also known to be a bottleneck for many applications executing on GPUs. By limiting the number of times results are transported across the PCIe bus in the TLM algorithm, we were able to optimize the calculation time by an order of magnitude (Figure 3). Notice in Figure 3 that the time per step for CPUs remains fairly constant from 10 to 1000 steps, whereas the GPU results show an order of magnitude decrease in time per step. This illustrates the importance of increasing the computation to communication ratio when using GPUs as a coprocessor. In Figure 3, the cpu-opt and gpu-opt lines refer to the use of the shuffled grid optimization method that combines four single precision floating